半整数分频器 求助

小弟刚入门 对于代码原理不是很懂 尤其是仿真后temp1波形更是觉得匪夷所思 望朋友们能热心帮助

// 代码功能 实现1.5分频

module div_half(div,clk);

output div;

input clk;

reg count=0;

reg div;

reg clk_temp2=0, clk_temp3=0;

assign clk_temp1 = clk^clk_temp2;

always @ (posedge clk_temp1)

begin

if (count == 0)

begin count <=1; clk_temp3<=1; div<=1;end

else

begin count <= count - 1;clk_temp3<=0; div<=0;end

end

always @(posedge clk_temp3)

begin

clk_temp2<=~clk_temp2;

end

endmodule

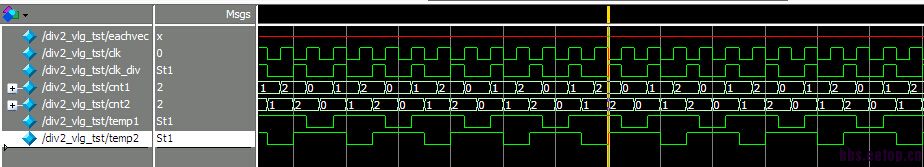

仿真后输入输出波形 及代码中变量波形:

//任意分频系数为 N+0.5 的占空比为1:1的非整数分频器

module div2(clk, clk_div, cnt1, cnt2, temp1, temp2);

input clk;

output clk_div;

output reg [31:0]cnt1, cnt2;

output reg temp1, temp2;

parameter N=1;

initial begin temp1=0; temp2=1;cnt1=0;cnt2=2*N;end

always @(posedge clk)

begin

if(cnt1==2*N) begin cnt1<=0; end

else begin cnt1<=cnt1+1; end

if(cnt1==0) begin temp1<=1; end

if(cnt1==N+1) begin temp1<=0; end

end

always @(negedge clk)

begin

if(cnt2==0) begin temp2<=0; end

if(cnt2==N) begin temp2<=1; end

if(cnt2==2*N) begin cnt2<=0; end

else begin cnt2<=cnt2+1; end

end

assign clk_div=temp1&&temp2;

endmodule

// Testbench

`timescale 1 ns/ 1 ns

module div2_vlg_tst();

// constants

// general purpose registers

reg eachvec;

// test vector input registers

reg clk;

wire clk_div;

wire [31:0] cnt1;

wire [31:0] cnt2;

wire temp1;

wire temp2;

div2 i1 (

.clk(clk),

.clk_div(clk_div),

.cnt1(cnt1),

.cnt2(cnt2),

.temp1(temp1),

.temp2(temp2)

);

initial

begin

clk=0;

forever #5 clk=~clk;

end

endmodule

问题解决了?既然解决了,给大家报告下最终解决结果以及方法