FPGA中高性能异步复位信号的实现

时间:10-02

整理:3721RD

点击:

你是否曾想过,你的fMAX居然是被异步复位拖慢的吗?!?!

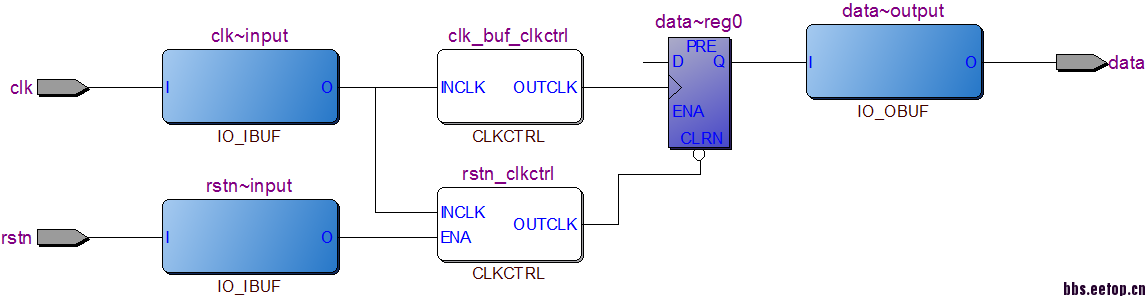

假如你的系统中有同步撤离的异步复位信号(如果你没听过同步撤离,那你可以离开本帖了。),那工具默认的设置很可能会实现成下面这个样子:

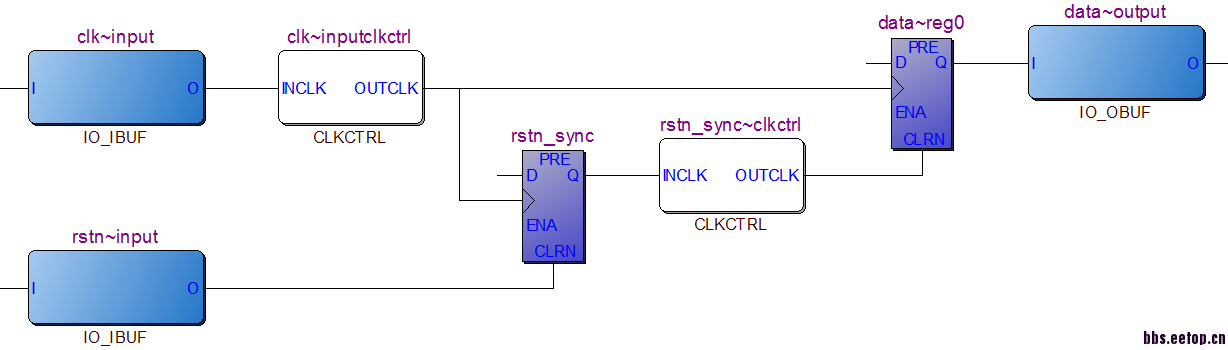

低性能实现方法一:级联的全局缓冲

在Fitter的默认策略里,同步撤离后的异步复位信号会再次进入一个全局缓冲,这样到寄存器时钟端的路径经过了【一个】全局缓冲,而到寄存器复位端的路径经过了【两个】全局缓冲。对Stratix III C2/C4器件,复位比时钟慢2.4ns/3ns,直接将它们的fMAX限制在400MHz/333MHz。

Recovery Slack: -1.4ns (Stratix III C2器件,1ns时钟周期,Slow 85C)

LZ近期在Stratix III -3器件上的一个设计有四千多个寄存器,在常温下同时跑750MHz,还有大量的异步复位。那么LZ是怎么做到的呢?请慢慢看。

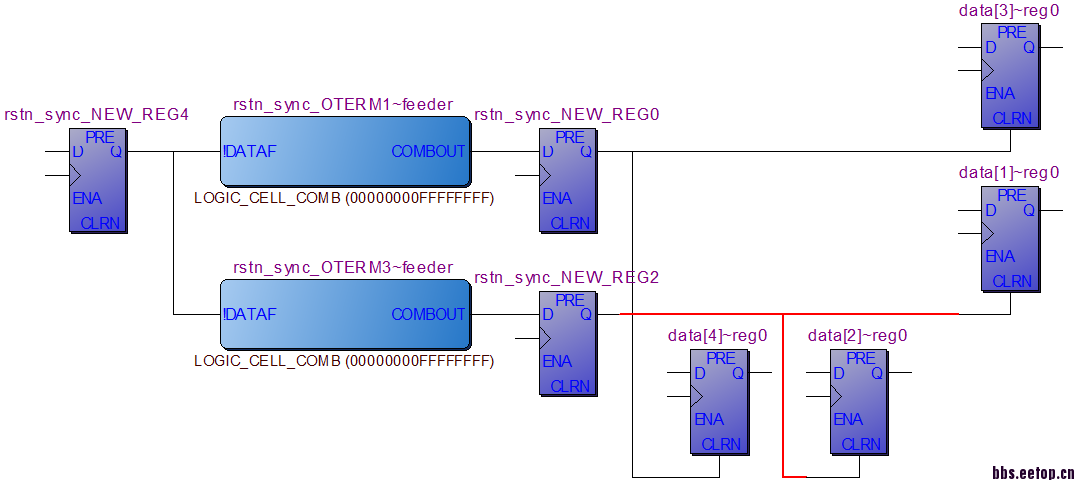

低性能实现方法二:开启物理综合中的“自动异步复位流水线处理”

Quartus针对这个问题,专门做了一个物理综合引擎即“Automatic Asynchronous Signal Pipelining”,开启之后异步复位不走全局缓冲,而是变成了本地的一颗流水线树。但这个方法有三个缺陷:1.占用大量的LUT和本地走线资源,拖慢综合速度。2.流水线树本身的时序仍有可能成为瓶颈。3.这个算法在实际综合中常由于各种原因不被“激活”。

Recovery Slack: -0.46ns (Stratix III C2器件,1ns时钟周期,Slow 85C)

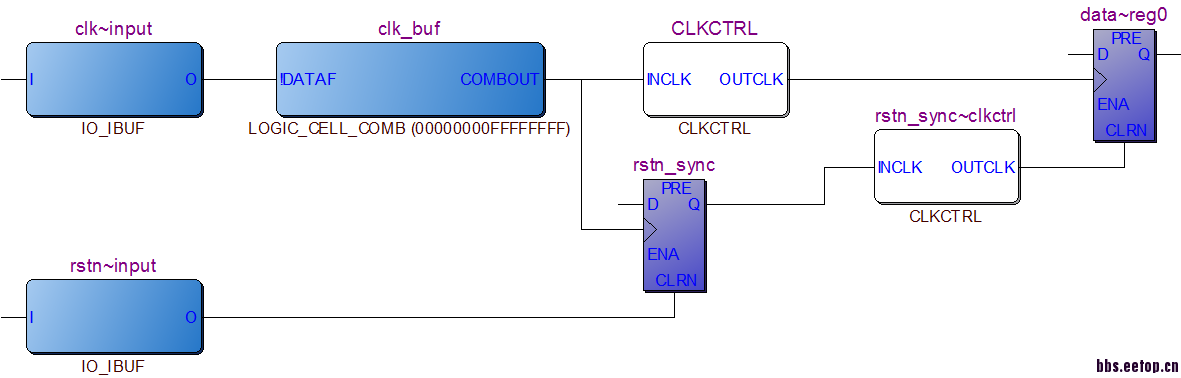

低性能实现方法三:用本地时钟进行同步撤离,再将时钟和复位一起拖进全局缓冲

通过将输入时钟拖到本地LUT做同步撤离,再和复位一起进入全局缓冲,确实可以解决限制fMAX的问题,在ASIC里是标准的做法,但用在FPGA上有两个重大缺陷:1.时钟拖到LUT再进入全局缓冲的延时太大,相当于没有用专用时钟引脚了。2.时钟进入本地LUT,Jitter和占空比都会变差。

Recovery Slack: 0.079ns (Stratix III C2器件,1ns时钟周期,Slow 85C)

Removal Slack: 0.133ns (Stratix III C2器件,1ns时钟周期,Fast 0C)

**************************************************

***** 以上是三种低性能的异步复位实现方法,好孩子不要学喔 *****

**************************************************

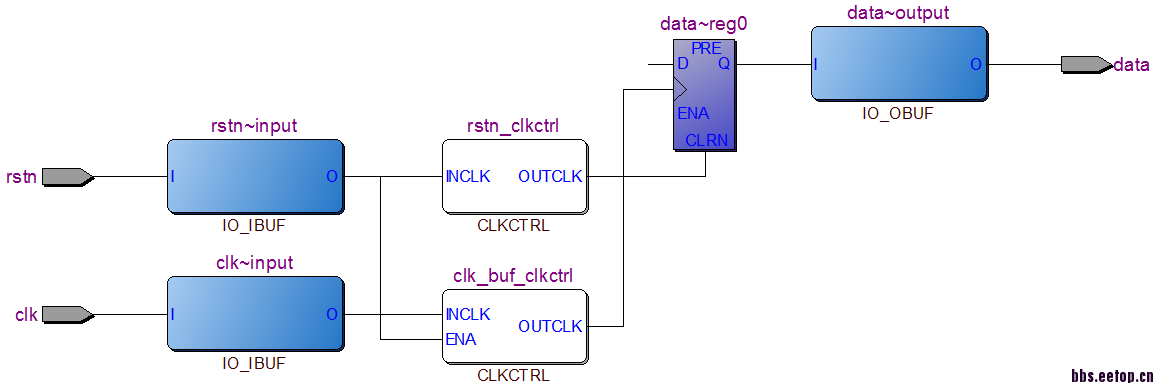

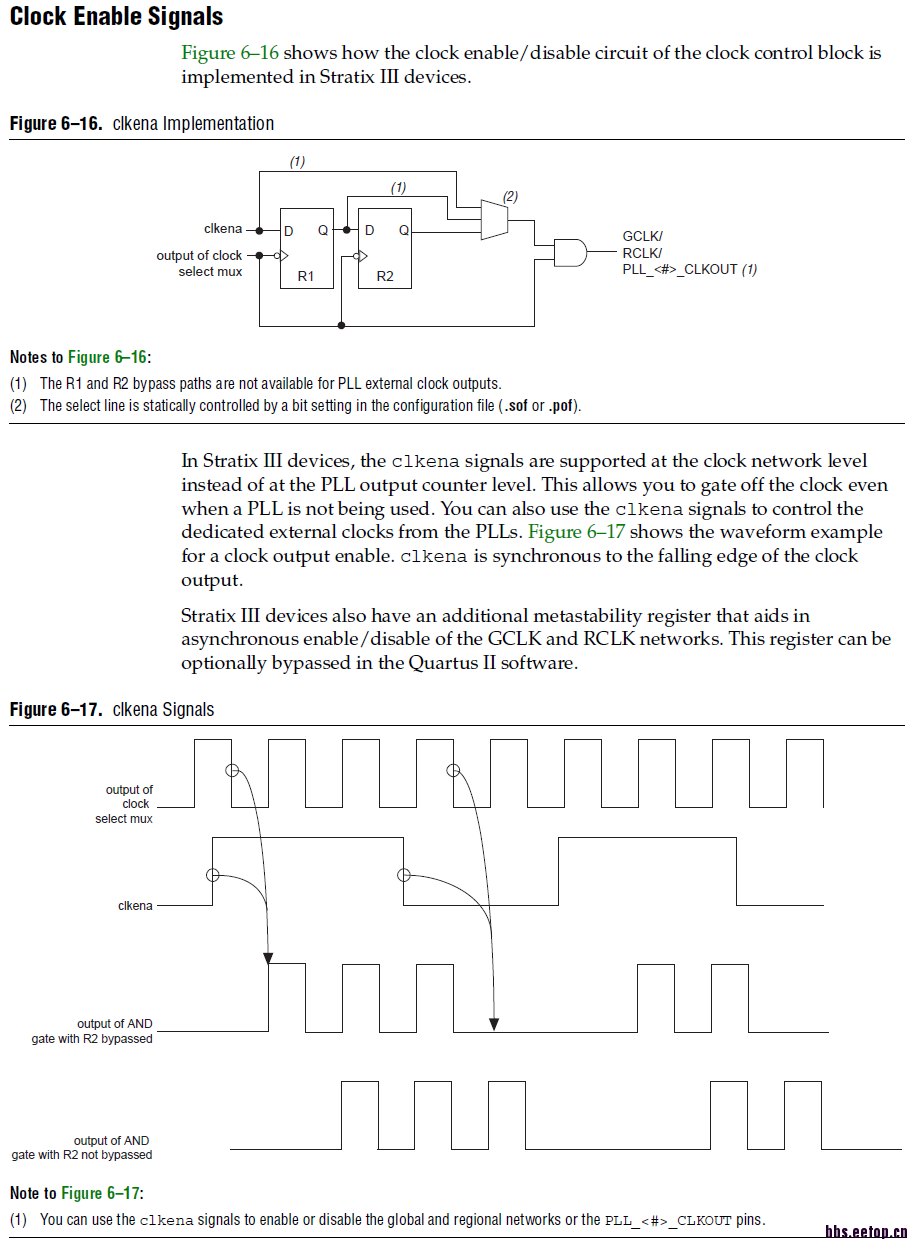

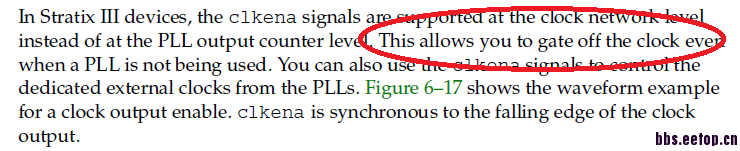

高性能实现方法一:复位期间将时钟关掉

在复位期间将时钟Gate掉后,Recovery/Removal的时序关系就不存在了,自然没有冲击fMAX的问题。在这里需要启用CLKCTRL中自带的两级寄存器以实现通过ENA的无毛刺门控。不过这个方法有个很大的局限性:这个时钟驱动的所有寄存器必须都用这个异步复位信号。如果存在多个异步复位信号,或者存在没有复位的寄存器,那这个方法就不太适用了。

高性能实现方法二:时钟门控后作为异步复位信号

这个新颖的方法非常适合FPGA,按此方法实现的复位不是一个电平而是跟时钟一样的脉冲:

- ___ ___ ___ ___ ___

- CLK ___| |___| |___| |___| |___| |___

- |← →|

- ___ __Removal__ Recovery

- RST ___| |___| |___| |___________________

- ↑Gate

Recovery Slack: 0.33ns (Stratix III C2器件,1ns时钟周期,Slow 85C)

Removal Slack: 0.427ns (Stratix III C2器件,1ns时钟周期,Fast 0C)

这里是altera的时钟使能模块,是一个硬核。

请问为啥FPGA不能用门控时钟啊?

求指点

我就想请教一下Altera做这个功能出来是干嘛的呀?

这个模块做出来是实现低功耗,什么睡眠模式的。呵呵

这里算不得门控时钟,你可以看手册,这描述中没有用到门控时钟的概念。这个altera的一个硬核,算是一个时钟使能电路。

。

学习了,不明而利啊。

写得不错 学习了

学习了,

一般 异步复位的时序定义为false path就可以避免异步复位影响fmax了,是这样吧?

应用异步复位的同步撤离的设计目的是为了代替同步复位,减小资源消耗么? 不太明白为什么这么纠结?