xilinx CORDIC 取对数

时间:10-02

整理:3721RD

点击:

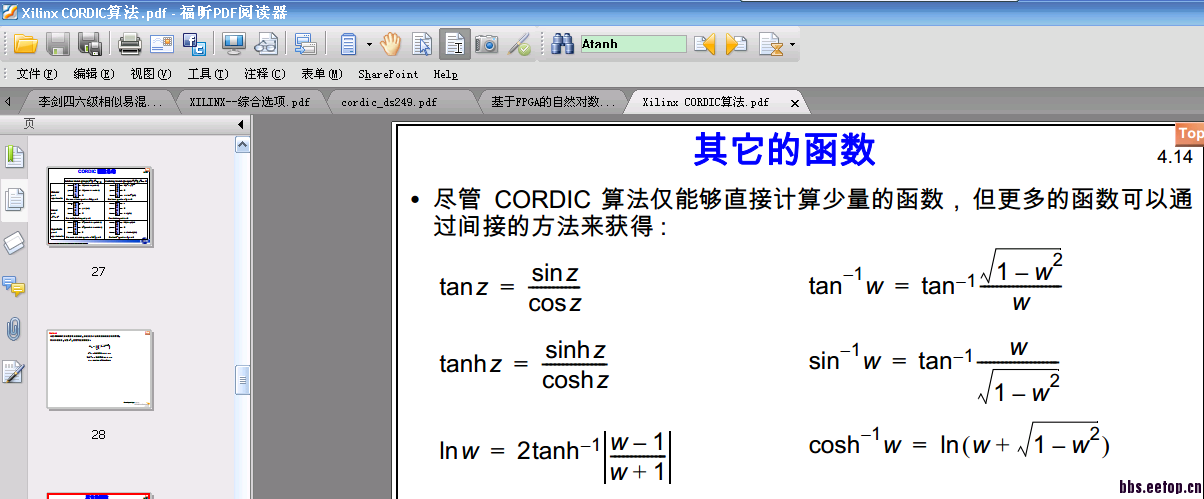

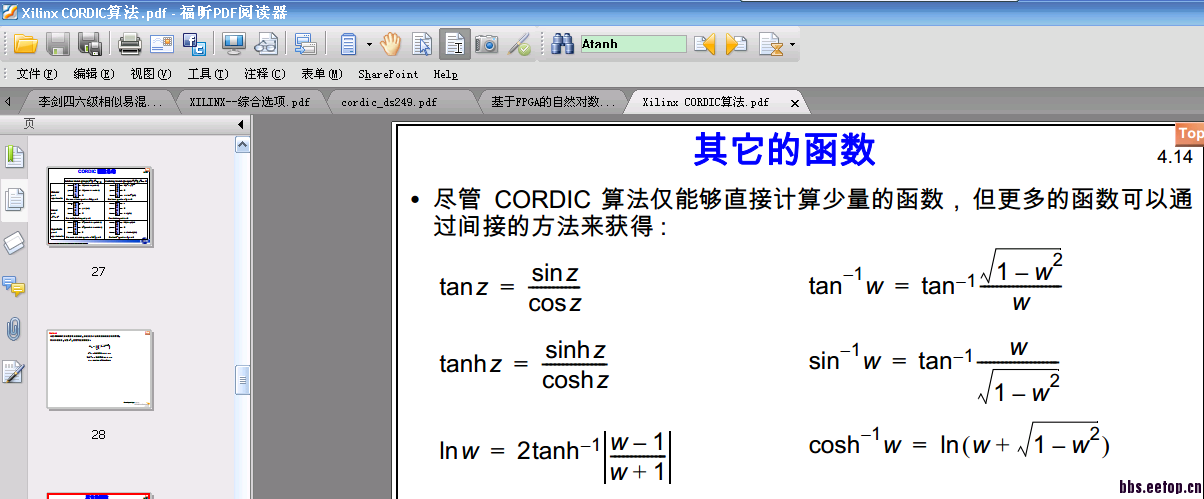

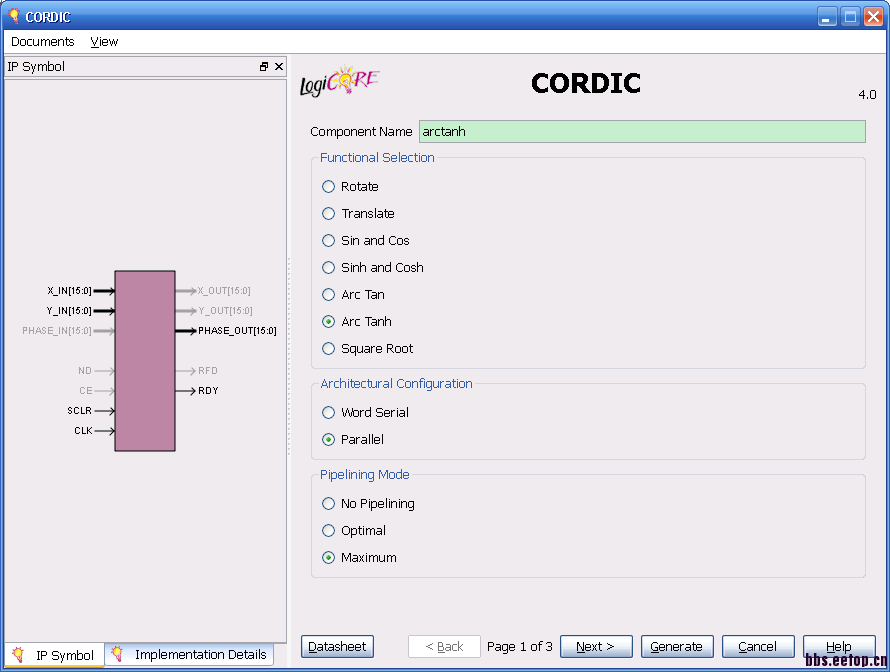

我想看看怎么取对数。我看到有篇PPT说怎么取对的

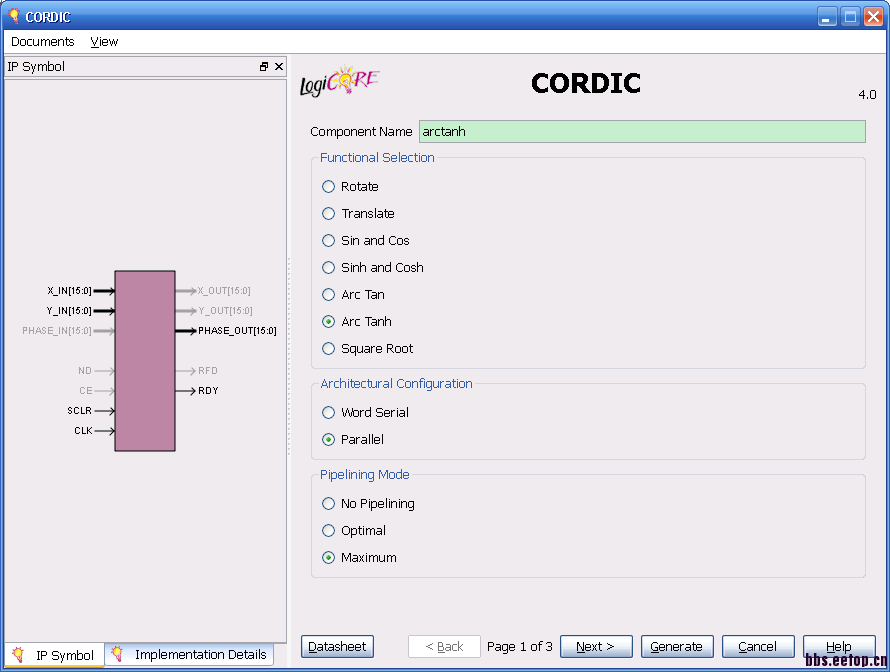

我就用了IP core

代码如下。

module qulog(

input clk100m,

input sys_rst,

input [15:0]data_in,

output reg [15:0]data_out_reg,

output reg data_out_flag

);

wire [15:0] data_inX,data_inY;

wire rdy;

wire [15:0] phase_out;

assign data_inX=data_in+1;

assign data_inY=data_in-1;

always @(posedge clk100m )

begin

data_out_flag<=rdy;

data_out_reg<=phase_out;

end

arctanh arctanh1 (

.x_in(data_inX), // Bus [15 : 0]

.y_in(data_inY), // Bus [15 : 0]

.phase_out(phase_out), // Bus [15 : 0]

.rdy(rdy),

.clk(clk100m),

.sclr(sys_rst));

endmodule

testbench

module qulog_test;

// Inputs

reg clk100m;

reg sys_rst;

reg [15:0] data_in;

// Outputs

wire [15:0] data_out_reg;

wire data_out_flag;

// Instantiate the Unit Under Test (UUT)

qulog uut (

.clk100m(clk100m),

.sys_rst(sys_rst),

.data_in(data_in),

.data_out_reg(data_out_reg),

.data_out_flag(data_out_flag)

);

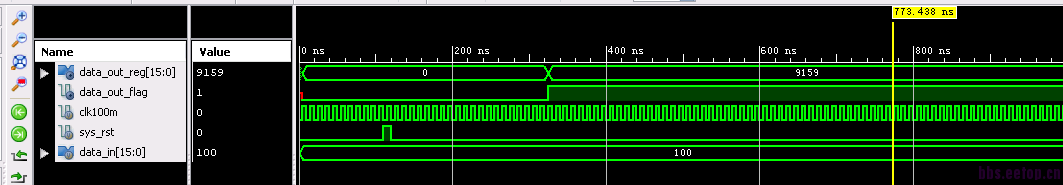

always #5 clk100m=~clk100m;

initial begin

// Initialize Inputs

clk100m = 0;

sys_rst = 0;

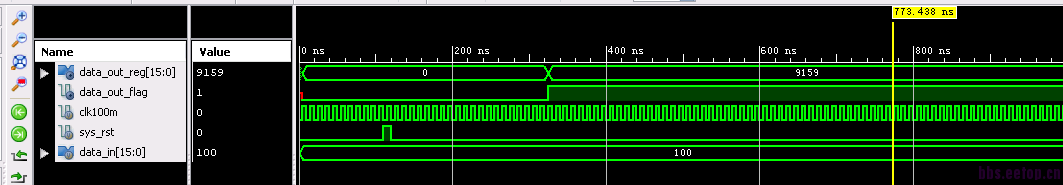

data_in = 100;

// Wait 100 ns for global reset to finish

#100;

#10

sys_rst=1;

#10

sys_rst=0;

// Add stimulus here

end

endmodule

出来的数不对啊

求大神指导。

我就用了IP core

代码如下。

module qulog(

input clk100m,

input sys_rst,

input [15:0]data_in,

output reg [15:0]data_out_reg,

output reg data_out_flag

);

wire [15:0] data_inX,data_inY;

wire rdy;

wire [15:0] phase_out;

assign data_inX=data_in+1;

assign data_inY=data_in-1;

always @(posedge clk100m )

begin

data_out_flag<=rdy;

data_out_reg<=phase_out;

end

arctanh arctanh1 (

.x_in(data_inX), // Bus [15 : 0]

.y_in(data_inY), // Bus [15 : 0]

.phase_out(phase_out), // Bus [15 : 0]

.rdy(rdy),

.clk(clk100m),

.sclr(sys_rst));

endmodule

testbench

module qulog_test;

// Inputs

reg clk100m;

reg sys_rst;

reg [15:0] data_in;

// Outputs

wire [15:0] data_out_reg;

wire data_out_flag;

// Instantiate the Unit Under Test (UUT)

qulog uut (

.clk100m(clk100m),

.sys_rst(sys_rst),

.data_in(data_in),

.data_out_reg(data_out_reg),

.data_out_flag(data_out_flag)

);

always #5 clk100m=~clk100m;

initial begin

// Initialize Inputs

clk100m = 0;

sys_rst = 0;

data_in = 100;

// Wait 100 ns for global reset to finish

#100;

#10

sys_rst=1;

#10

sys_rst=0;

// Add stimulus here

end

endmodule

出来的数不对啊

求大神指导。

有这个CORDIC的内核?我最近在写一个atan2函数,不过我用的是查表法。

想知道 arctanh 中的sclr是negedge还是posedge? 因为你的测试程序默认它是posedge

有呀。我用的span3A DSP这个芯片就有。 sclr 应该是 posedge的。不过我不管输入啥数据。这输出都不变啊。我都不知道咋使用这个IPcore了。按照datasheet实例输入,结果和datasheet说的结果不一样

assign data_inX=data_in+1;

assign data_inY=data_in-1;

这里应该不是直接加减1

例如迭代16次,那么1应该对应2^-16