关于V7的DDR3问题

时间:10-02

整理:3721RD

点击:

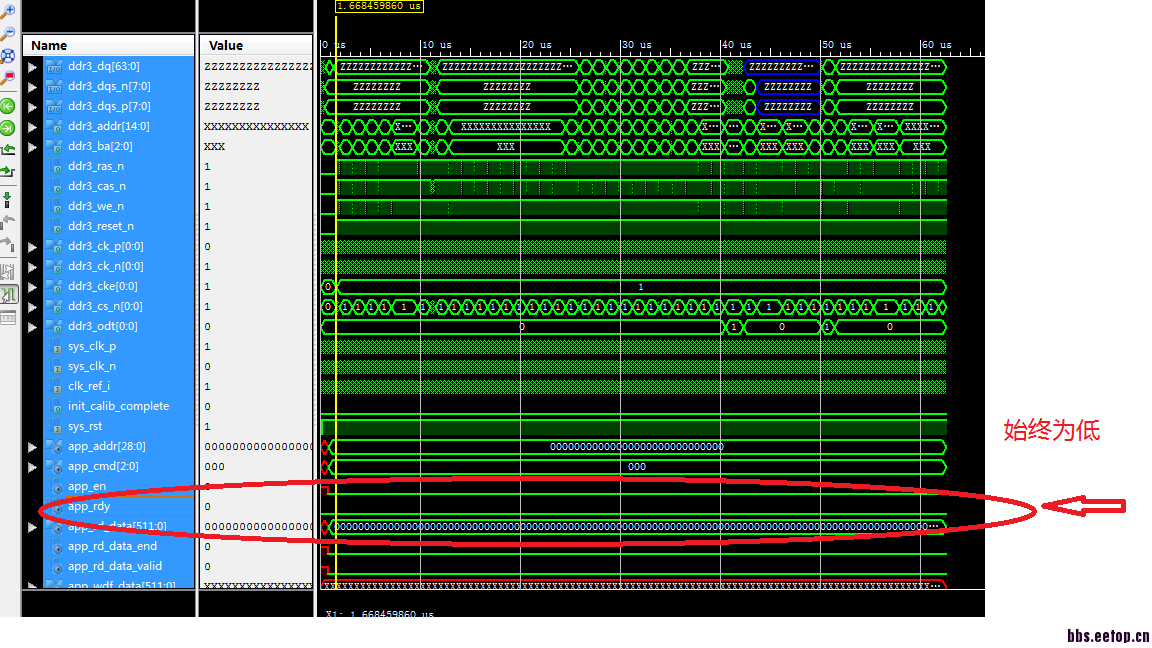

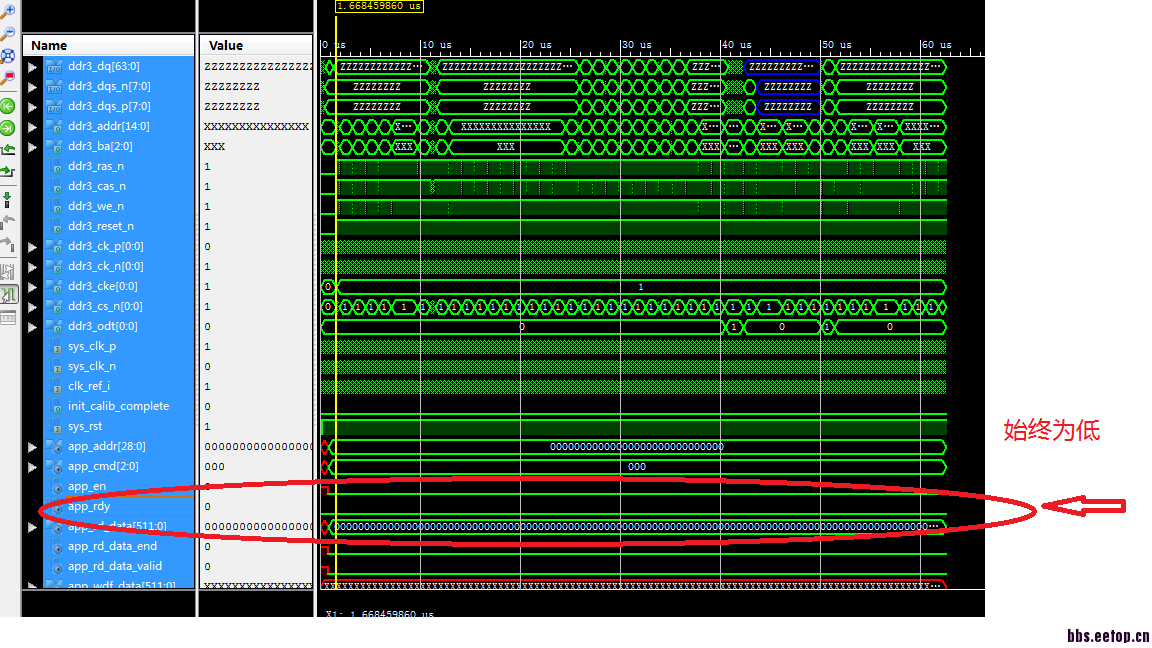

最近在调V7 485t的DDR3,用的ISE14.4,MIG1.8 ,生成的IP核无论仿真还是板测,其中的app_rdy这个信号始终为低电平,数据手册说原因有两个,一是正在读或者写,二是phy还没有复位好。上电复位后app_rdy信号应该为高的,但是从来都是低电平。

求教高手,不胜感激!

求教高手,不胜感激!

看看它的复位信号有效是高电平还是低电平?

DDR3控制器复位可设,我设的是低复位。example design 我仿真出结果了,仿真了120us才出来的,用了半小时。

自己写的user design仿真了220us , init_calib_complete 以及app_rdy始终不拉高。

求教!

同问,我也在v7485T上遇到这个问题了,app_rdy一直为低,小编问题解决了吗?

init_calib_complete没拉高,那就是上电后校验没有成功呗,用ip核自带的example_design一步步的找原因吧,ug586 ddr3部分由hardware debug