请教关于CRC的实现

时间:10-02

整理:3721RD

点击:

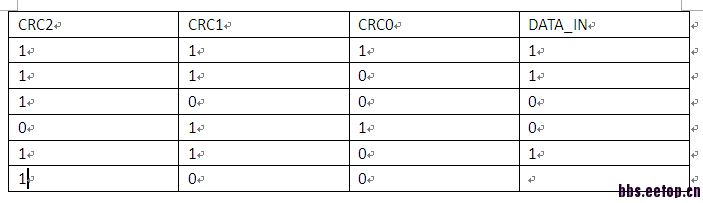

以生成多项式x^3+x^1+1(即4’b1011)为例,如果是数据5‘b11001;

设CRC初值为3‘b111,

CRC0<=DATA_IN ^ CRC2;

CRC1<=DATA_IN ^ CRC2 ^ CRC0;

CRC2<=CRC1;

当数据输入完后结果是3'b100,这个数据对吗?感觉不错啊

反正在用同样的方法做以太网的CRC32时得到的数据,就跟用ALTERA的MAC核自动生成的CRC不同,不明白怎么回事!

网上好像能下载到相关的源代码!

有没有高人指教一下,怎么算都不对,网上还有一种方法,查表法也试过,还是不对,受不了了

crc32 <= mytab[crc32[7:0]^tx_data[12095:12088]] ^ {8'h00,crc32[31:8]};

tx_data <= {tx_data[12087:0],8'h00};

其中mytab是表,正反表都试过,没一个是对的

www.outputlogic.com

这个是将所有的数据一下计算出来 ,对于长数据这个参考意义不大啊,数据太多的话不可能这样去算吧

可以用并行计算的方法,简化CRC的设计

我自己来回答吧:

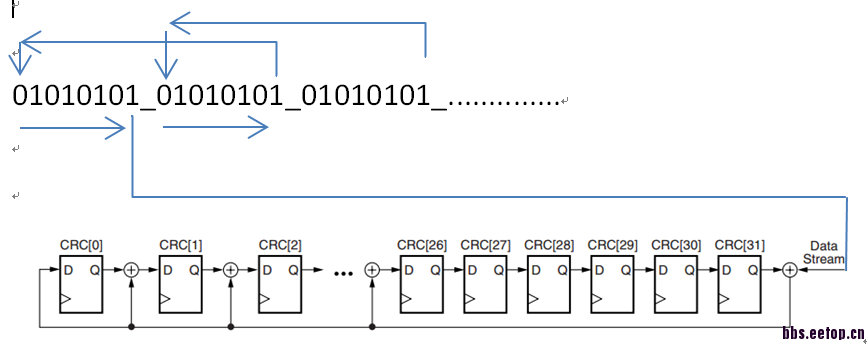

第一步将需要传输的数据按如下的顺序通过寄存器:

2,当数据传输完成后,对CRC里的数据以字节为单位倒序后再取反,如下

CRC[7:0] = ~CRC[0:7];

CRC[15:8] = ~CRC[8:15];

CRC[23:16] = ~CRC[16:23];

CRC[31:24] = ~CRC[24:31];

3,经过以上处理后得到的CRC即为以太网发送里需要的CRC