关于Verilog的多重赋值

时间:10-02

整理:3721RD

点击:

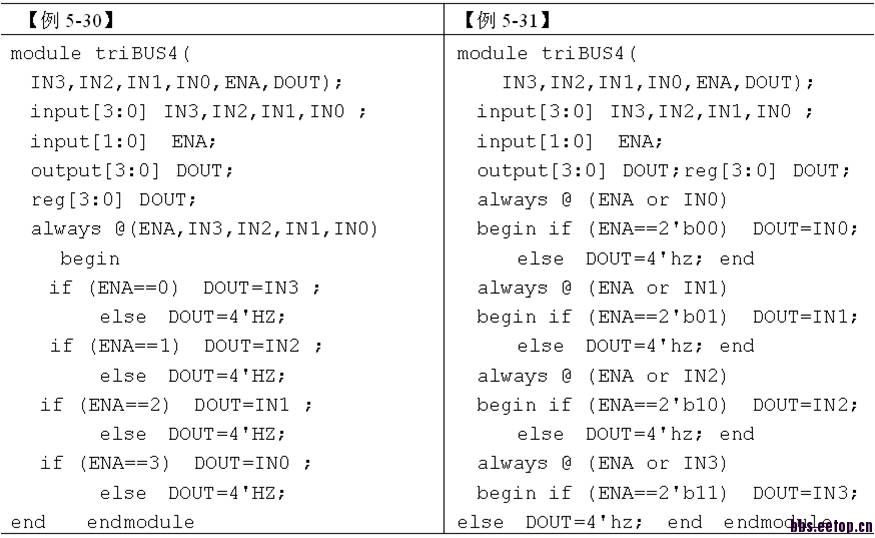

本人也有好几年Verilog的工程经验了,不过最近在看潘松的教材,其中例5-31(上图右边)使用多重赋值实现三态总线,首先这种风格我觉得在实际中肯定是不太好的,读起来别扭,分析起来也麻烦,直接用一个case语句在always块搞定即可,但潘松又解释了一大段说这种是可以的,我没具体仿真,像他这种多重赋值没有问题吗?如果ena发生变化,这4个块会同时执行,只有一条语句执行结果不是高阻态,其它都是高阻态,Verilog会自动将那些高阻态的结果忽略?哪里有权威解读?我记得在RTL代码中是要严格避免多重赋值的

三态总线本来就是多个BUFZ输出连在一起的,只不过逻辑保证不能同时有超过一个在输出,其他高阻。

三态总线只有一个BUFZ吧,先用数据选择器选择输出信号,再到三态门,多个三态门没有意义

不建议多重复值,并不是所有的仿真器和编译器都支持这种风格

多重赋值是什么?第一次听这个概念啊

我也不认为潘松的这个例子写得好,但这样做到底行不行?Verilog是如何对待的?

5-31也就是仿真结果上跟5-30一致而已了。

但是这两者想表达的现实意义是完全不同的。

作为RTL的话,5-31的风格基本上所有的公司都是不允许的。可读性、可维护性太差。工具也不一定会支持。

写书作为工程,做了工程再写书,两者什么区别……