chipscope影响布局布线,会不会影响逻辑功能

板上管脚输入时钟是245.76M,然后通过DCM分频到153.6M。上星期发现由于cdc加的信号多且深度大,导致PAR出来的最大时钟频率达不到153.6M,看关键路径是cdc加入的信号造成的,然后就把cdc深度从8192减少到1024,信号宽度也减小了,PAR出来的最大频率能达到220多M。

但是现在上板遇到一个很奇怪的问题,修改之后PAR时钟频率变大了,但是我传输的数据就在半路堵住了,没有发送成功。由于cdc深度减小且信号少了,我看不到错误位置。这时我又把cdc信号的深度变为8192,抓了很多的信号,PAR出来的最大时钟平率为100M这样(关键路径为cdc的路径),数据又能正常传输了!

这个现象哪位大神可以帮我解释一下~这个情况我的switch是不是能跑在153.6M呢(以前78M的时候没有出现过这个问题,无论什么样长度的数据都能正常发送)?我在ucf里面也把153.6M的那个clk加了约束,也没有报错!求帮助!

我来顶贴!

检查下你的input, output pins加了delay约束没有,进来的数据是不是锁在IOB上,数据被时钟采集之前有无组合逻辑,数据送出最后一级是寄存器输出,还是组合逻辑输出?

像这种加了identify或chipscope后功能反而正常,不加不能用的情况我也用过,一般这样即使能正常工作也只是偶尔布线的结果是正常的,因为加了多的其它资源反而把结果“挤”得比较好。因为中间的数据一般都是寄存器间的关系,应该算正常;输入输出的pin间输出容易出问题。另外,检查下你的代码风格,比如控制信号之类的,要是一个使能信号本来采的位置不对,结果因timing slack结果延后采了拍反而正常了也有可能,会说明代码健壮性并不过关。

谢谢你的回复!希望你能再帮我看一下问题,真的非常感谢

①input和output都没有加什么delay约束,delay约束有什么用呢?

②我的数据是片间传输的,通过一个高速串行接口 ,rxn、rxp,txn和txp 看map报告IOB properties类型写的是IPAD和OPAD。我检查过跨片输入的数据是没有错误,但是到了接收端这边就出现错误;

③我分了好多段对数据进行了采样,因为我要看到底在哪一段出的错,每段采集之前是有组合逻辑的,这会有什么影响呢?

④我的数据送出的最后一级是寄存器输出。

⑤为什么我在78M的情况下没出现这种问题呢?

你当时遇到这种问题是怎么解决的呢?对你的回答再次感谢

①input和output都没有加什么delay约束,delay约束有什么用呢?具体delay的作用也可以从论坛上下载点资料去看,input, output不加约束,那对这块的时序分析是不会做的,如果时序不满足你也不知道。

另外,input/output delay的信息是相对于与FPGA相连接的另外的芯片的对应PIN管脚的信息,你不告诉FPGA对端的PIN信息是什么,那FPGA就只能按默认的布线,布好布坏随机的。

②我的数据是片间传输的,通过一个高速串行接口 ,rxn、rxp,txn和txp 看map报告IOB properties类型写的是IPAD和OPAD。我检查过跨片输入的数据是没有错误,但是到了接收端这边就出现错误;

如果你用了SEDERS,比如1G, 2.5G的串行速度,那最基本的发送接收测试、环回测试功能应该具有,以备出错时定位使用。现在你已经检查出现错误,那要更一步分析,比如一边分递增序列,看另一方是什么样的,出现什么样错误来定位。

③我分了好多段对数据进行了采样,因为我要看到底在哪一段出的错,每段采集之前是有组合逻辑的,这会有什么影响呢?

对数据采集一般使用寄存器输出为好,当然,要是普通信息,组合输出也没啥问题,因为毕竟只是看看,就算有错也能大体起到定位的作用。但是这样可能把原代码设计里的组线等做差了,甚至出现功能错误,就是说你插入chipscope导致工程跑错。就是你的问题1K深度出错,8K正常的情况也是可能的。

④我的数据送出的最后一级是寄存器输出。

这是较好的风格,一般还会用planAhead看看是否锁在IOB上,也就是最后一级寄存器的布的位置在IOB旁边的OLOGIC里。

⑤为什么我在78M的情况下没出现这种问题呢?

太正常不过了,时钟频率低不容易出问题,低于50M的时钟连约束都不加都能跑得好好的,超过100M约束、代码风格、布线等就重要了,超过200M时序不过要很重视了。

你当时遇到这种问题是怎么解决的呢?对你的回答再次感谢

谢谢你耐心的回答!

①SEDERS是工作在9.8G的,之前对其单独做过递增序列的收发测试,是没有误码的,然后接上switch以后,由于数据要有头片和标志位什么的,就没有用递增序列来做了。

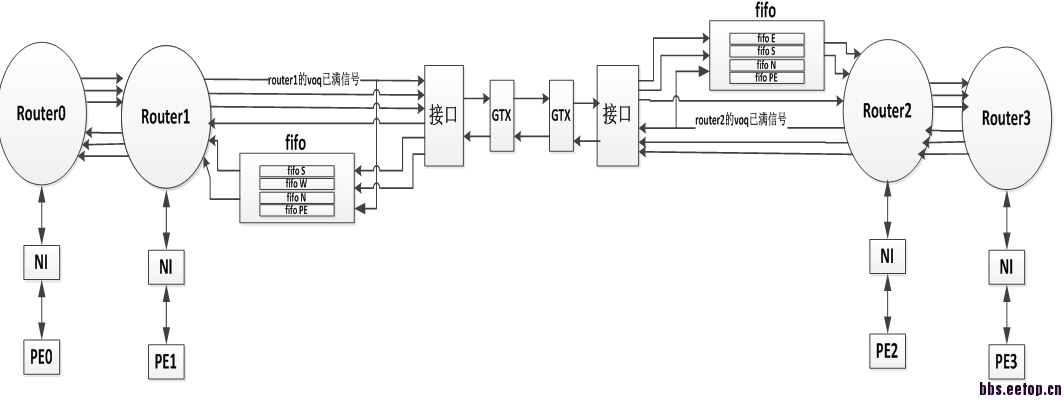

②我还发现一个问题,我的设计架构如下图。本来为了提高PAR出来的时钟频率,chipscope只抓到接口模块的数据,因为没有错误的话数据就会循环发送,不会发生堵塞。但是当我发现数据有堵塞时,就在chipscope一级一级的往下抓信号,当把接口模块,fifo模块和router模块里面重要的信号加入chipscope后,再次下板,就发现数据能正常传输了,没有误码没有堵塞。不过也是时好时坏,把发端数据包长度变一下,又很容易出错了。

这个情况跟你讲的“对数据采集一般使用寄存器输出为好,当然,要是普通信息,组合输出也没啥问题,因为毕竟只是看看,就算有错也能大体起到定位的作用。但是这样可能把原代码设计里的组线等做差了,甚至出现功能错误,就是说你插入chipscope导致工程跑错。就是你的问题1K深度出错,8K正常的情况也是可能的”类似。E_443QS.jpg)

根据你的回答,我觉得我要先去下点时序约束的文档学习一下!谢谢了~

刚才图片好像没上传成功...这是我设计的大致架构。

要么你还是再发下序列看看,以router1发送递增数据,直接到GTX环回,看 FIFO之前收到的如何,再试左边发右边收,右边发左边收的,这个与你之前直接在GTX上发送序列还是有差别的,现在相当于是有效负载测试,之前是整体直接看序列。

关注一下出错的类型,比如是数据少发重发,FIFO空满有异,还是数据错位、接收就不正常之类的,因为你之前已经测过序列,数据错位和接收不正常的可能性小点,重点关注多数少数看看。

学习了

学习了