如何消除加法进位产生的延迟啊

wr_addr <= wr_addr + 1;

因为地址是10位的,所以在产生wr_addr的时候 ,需要多次进位,导致了时序不满足

这种情况该怎么办呢

从时序分析来看,确实没有用到进位链,难道你的芯片用满了,还是代码原因?

请把代码贴出来看一下、

我用v5的芯片做加法器,也没有生成进位链,不知道怎么回事

这个是接收千兆网卡传过来的数据, 根据protocol_cmd 是否等于DD22DD可以分为两种数据类型,所以有两种起始地址和地址递增的方法

always @ (posedge prxc,negedge rst_n)

begin

if(!rst_n)

ethernet_receive_wr_addr_lsb <= 0;

else if(((rxd_cnt == 55)&&(protocol_cmd != 24'hDD22DD)))

ethernet_receive_wr_addr_lsb <= 0; //数据类型为1的起始地址

else if((rxd_cnt == 55)&&(protocol_cmd == 24'hDD22DD))

ethernet_receive_wr_addr_lsb <= protocol_color; //数据类型为2的起始地址

else if(ethernet_receive_wr_en&&(protocol_cmd == 24'hDD22DD))

ethernet_receive_wr_addr_lsb <= ethernet_receive_wr_addr_lsb + 4; //数据类型为2的地址递增方法

else if(ethernet_receive_wr_en)

ethernet_receive_wr_addr_lsb <= ethernet_receive_wr_addr_lsb + 1; //数据类型为1的地址递增方法

end

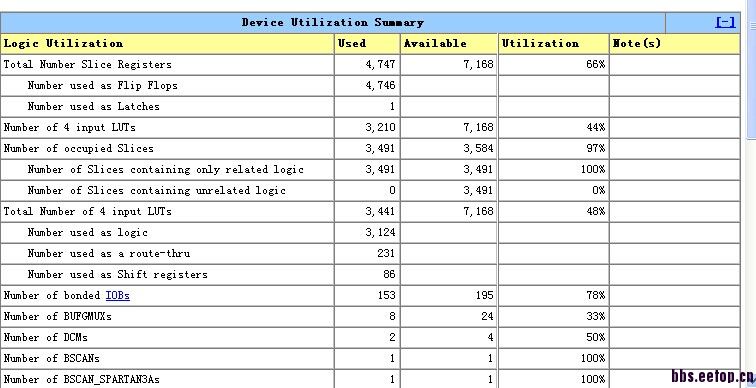

PS:资源利用率如下[img]file:///C:\Documents and Settings\Administrator\Application Data\Tencent\Users\313951065\QQ\WinTemp\RichOle\DW`FLI97Z[[9QGO37NP)Z@6.jpg[/img],没有添加区域约束之类的

1.你的资源利用率不高,应该不是资源分配不足的问题

2.ethernet_receive_wr_addr_lsb既有加4又有加1,可能这是导致不能使用进位链的原因

3.建议:如果可能的话,使用两个加法器,一个计数器负责加1的加法操作,一个计数器负责加4的加法操作。然后再把这两个加法器加到一起,应该就可以用到进位链了。不过资源占用率就上去了,这是一个弊端。

非常感谢您的指导和建议!我现在仅仅让地址加1,就不会产生时序问题啦,应该是有时候加1,有时候加4的原因

那这样看来,如果要使用加法进位链,只能选择一种加法操作。这可能是xilinx的底层原因造成的。