两块FPGA用跳线连接是能否传输时钟信号

故请问各位有经验的工程师,能否在两块FPGA之间用导线传递时钟信号?

If your platform used the xilinx fpga chip. You can used the ODDR to do it.

速度不快可接, 但兩塊版子要共地

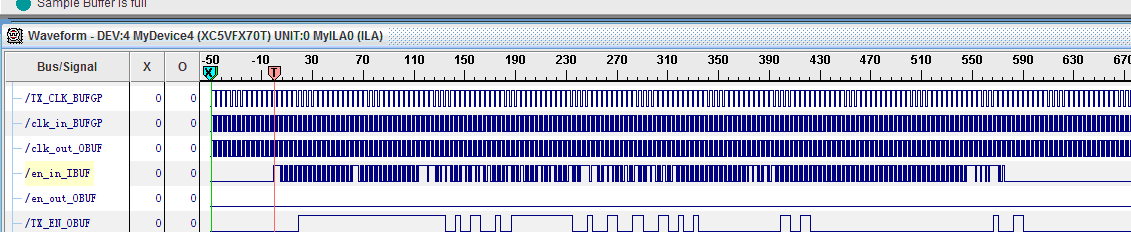

的确使用的是Xilinx的板子,查阅了ODDR,认为其主要作用是让输出时钟稳定,但是目前的状态是输出时钟chipscope显示稳定,输入时钟显示不稳定。 输入时钟是分配到一个普通IO管脚进入FPGA的,生成bit文件时会报错,但是被忽略了。不知把普通IO作为时钟输入时是否有什么办法使其质量更好。

传递的时钟是50M的,不知道能否算作速度不快。 其次是对于两块FPGA应该如何共地呢?

新手上路,有太多不懂的地方。

1. How do you to do you output clock.

2. The clock input must be into by the glck port. That is necessary for it. You can't used the normal gpio port.

50M還好, 我接過100M的

兩塊FPGA電源要共地, 我們的作法是有一塊母版, 上頭接兩塊FPGA, 電源要是同source

如果你已經是兩塊獨立的要透過bus溝通, 那可以把其中一塊的原始power路徑斷開, 另外設計power電路, 來源是另一塊FPGA版

另外要聽樓上大大說的, 你clock input端一定要用GCLK的, 會比較穩

我的设计逻辑详见另一个帖子:http://bbs.eetop.cn/viewthread.php?from=notice&tid=450784 FPGA1和FPGA2是通过跳线连接的

(FPGA1的clk_out、data_out、en_out、clk_in、data_in、en_in的引脚被分配到该板子上的Single-Ended Expansion I/O Connectors, FPGA2的相应input和output被分配到FPGA 2板子上的一些GPIO pins上,然后用跳线将这些pins进行连接,这些信号中就包括的clk)

所以说我的clk_in是通过普通IO口进入FPGA的,不知道如何规避这个问题,求指教。

還有一種更暴力的方法, 也是最快的

利用跳線, 將兩塊FPGA的地線通通連接起來, 而且盡可能的多連一些

這我也試過, 有時板子電源事前沒規劃, 或是客戶臨時要對接時, 會這麼搞

关于GCLK仍不太理解: 我的clk_in必须是由另一块FPGA输出的(因为我要同步输入的数据),而GCLK不是应该是由本块板子晶振源产生的才行吗?

我不知道是不是自己的理解仍不够透彻,不知道该如何处理从另一块板子来的clk,并通过本块板子的GCLK IO口进行输入。

你那塊要clock輸入的FPGA是自己設計的嗎? 如果是, 可以在pin assignment時將輸入腳位配置在GCLK(global clk)的input, 如果是第三方提供的, 不能自己配置腳位的, 那原始配置應該就已經是GCLK了, 因為這是基本的觀念

我覺得你現在應該要處理的是兩塊FPGA板共地的問題, 依經驗這對跳線訊號影響很大

Which type of the your fpga? Could you describe more detail of you platform?The debug will more effectively.

抱歉没有说明这些信息。两块开发板分别是Xilinx的ml505和ml605。 还有刚才那个链接貌似有问题:http://bbs.eetop.cn/thread-450784-1-1.html

两块板子都不是自己设计的,分别是Xinlinx的ml505和ml605。 板子上的FPGA GCLK IO 应该都是和板子上的晶振等连接好的, 从另一块板子上过来的clk_in是通过跳线连接PIN,PIN在板子上连接着FPGA 的GPIO,所以我不知道该如何让clk_in从FPGA 的GCLK IO口输入进来。

首先特别感谢,一直耐心帮我分析问题。 我刚才做了些实验,尝试让两块开发板共地,有了一些发现。

(前提:目前我只有两块开发板,没有办法按照方法1[母版,改变power路径等方式],多余的跳线我也只有2根,我在两块板子之间连接了一根跳线,分别连接两块板子的地)

(1)在没有连接地线之前:

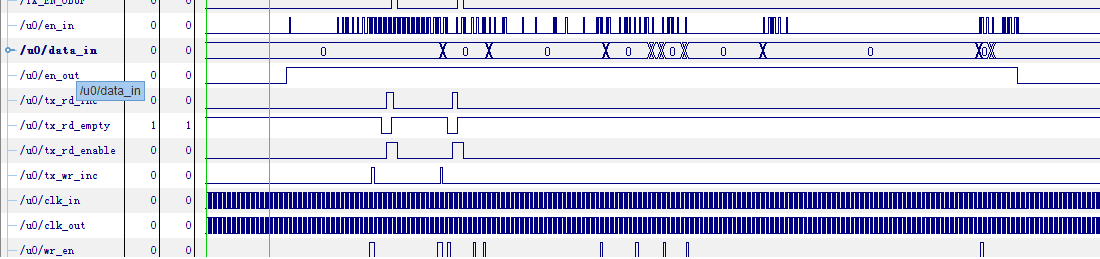

a. en_in会在en_out有效期间出现很多glitch(本应该一直保持低电平)【详见图1,第一行就是en_in信号】

b. en_in也会在其他时候经常出现glitch, 如果每次用en_in为1条件去抓取信号,几乎每次抓到的都是这种不该出现的glitch【详见图2,第二行就是en_in信号】

(2)在接了地线之后:

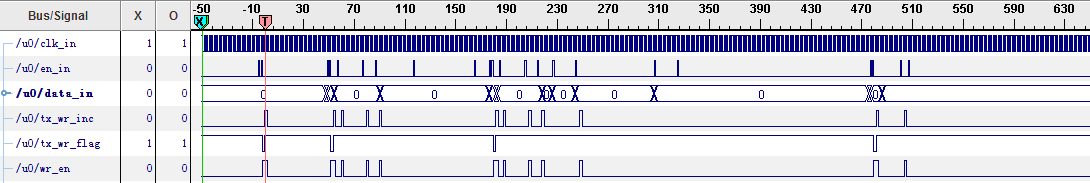

(1)中的a和b情况明显好转了很多,几乎每次以en_in为1条件去抓取信号时,都可以抓到我想要的en_in(理想情况是一段时间的持续高电平),但是又出现了新的问题,就是常常在这段高电平期间却出现了很多低电平glitch(着在没有接地线的时候几乎是没有的)【详见图3,第4行标黄的信号就是en_in】

感觉接了地线后,情况有明显变化,但是新出现的问题反而会导致我对信号的处理出现错误,不知道是否是共地做的不够彻底的原因。

PS :我之前在另一个帖子中也对情况有些说明,您可以参考一下(http://bbs.eetop.cn/thread-450784-1-1.html)

clock skew 會很難處理, 可能會發生 latch 不到資料的 case, 不建議如此.

是否本身用跳线在两块开发板上传递时钟信号这种行为本身就不可取。

这种通过跳线连接PIN输入给开发板的clk_in是否没有办法通过全局时钟网络进行处理?

1. Used the transceiver reference clock differential port to connect two fpga board. If the vertix-5 transceiver has the reference clock port that may be try it.

2. Modify your design by the asynchronous method to do it.

You can treat as fpga1 and fpga2 are two different clock domain.

So you can used the async method to do it. You just guaranty the fpga2 can latch correctly.

You may be used the IOB to attach the flip-flop on the IO pad. and fpga2 the first stage

flip-flop same as the fpga1 output port used the IOB to do it.如果用示波器戳出来不是方波,就需要解决阻抗匹配方面的问题。可尝试通过源端串电阻或终端并电阻解决。

最近比较忙,一直没有更新帖子,之前的问题都已近解决了。 (1)首先是两块FPGA之间要共地,这是必须的,刚开始我没有注意到。

(2)其次,造成glitch的最主要原因是因为两块板子用的不一样,连接的两块板子的PIN脚电压没有匹配,一边是3.3V,一边是2.5V,后来将电压匹配之后就好了。

(3)除此之外,仍然会很偶尔的产生一些小的glitch,后来换了更短一些的跳线来传递信号,所有问题都解决了。

因为我们设计的限制,必须要使用跳线来传递时钟,没有办法用全局时钟资源对时钟进行优化,但是100M的频率本身进行传递并不会产生我之前所认为的那些干扰,主要问题还是出在了自己身上。

非常感谢一直帮忙,反馈下我的结果与您分享。

最近比较忙,一直没有更新帖子,之前的问题都已近解决了。 (1)正如您之前给我提醒的,首先是两块FPGA之间要共地,这是我之前没有注意到的问题。

(2)其次,共地后仍有glitch, 后来发现造成glitch的最主要原因是因为两块板子用的不一样,连接的两块板子的PIN脚电压没有匹配,一边是3.3V,一边是2.5V,后来将电压匹配之后就好了。

(3)除此之外,仍然会很偶尔的产生一些小的glitch,后来换了更短一些的跳线来传递信号,所有问题都解决了。

因为我们设计的限制,必须要使用跳线来传递时钟,没有办法用全局时钟资源对时钟进行优化,但是100M的频率本身进行传递并不会产生我之前所认为的那些干扰,主要问题还是出在了自己身上。

非常感谢一直帮忙,反馈下我的结果与您分享。