关于xilinx的乘法器IP核的一个问题

用到xilinx的乘法器IP核,这里面的时钟频率和数据输入速率这两者之间有关系吗?是否时钟频率一定要大于等于数据输入速率呢?

如果输入信号的采样频率为125M ,而乘法器的时钟频率为5M ,就相当于进行了25倍的降采样,可以这样理解吗? 求教

时钟频率和数据输入速率?

没太懂?

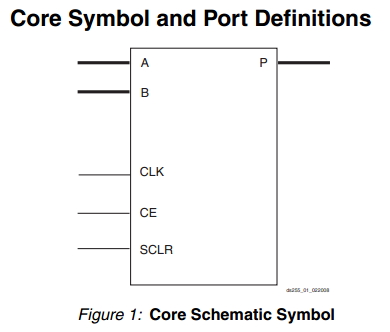

CLK就是乘法器的时钟频率 ,A,B两路为两路要相乘的信号。就是说CLK的频率是否要大于等于A,B信号的采样频率(即输入速率)

你的数据不在这个时钟域?MSPS和 MHZ 搞清楚 ,乘法器按照时钟流水计算,比如50M时钟25MSPS的数据,那么一个数据周期计算了两次,如果25M时钟50MSPS数据,那就看数据能不能满足建立保持时间,计算结果为25MSPS

谢谢,学习一下!

A B要属于CLK的时钟域内啊,兄弟

谢谢你的回答。 请问怎么知道是否满足建立保持时间?

如果输入信号的采样频率为125M ,而乘法器的时钟频率为5M ,就相当于进行了25倍的降采样?

不知道你要做什么,建议你将乘法器时钟用到和输入数据一样的时钟,输出数据你可以再抽取降到你要的5MSPS;因为即使输入时钟是5M,那么很多数据不会进行乘法操作,相当于乘法器时会做这个抽取,这样的时序一般目前器件都能满足,只是违背正确的做法。

一个小建议,

在了解建立、保持时间之前,先搞清楚“时钟都去哪儿了”?然后再了解下什么叫同步/异步设计。

逻辑设计中,时钟是个什么东东都不清楚的话,其它的东西看了用处不大

个人浅见,供参考!

36.25M的中频信号,经过125Msps的AD采样后,进行BPSK的解调,目前在做载波同步这块,125M的采样频率太高,想降下来,我知道可以在乘法器之后通过抽取来进行降采样,但我的想法是,能否在乘法器中完成降采样的过程?不知道能否实现

嗯,谢谢你的建议

125MSPS是5/4过采样吗? 信号在25M中心,带宽36.25M? 你这个降下来肯定要做抽取的啊,CIC FIR 等抽取滤波器,比较规范的方式,你这样直接抽取是不行的,抽取的原始信号带宽太大的话会导致频谱混叠,拿你没办法做同步的;

如果信号频谱小于5M,不严格把数据降到5 M可以直接抽取 ,噪声会混叠同步效果变差,就是多个数中选一个,加一个有效标志,始终还是125 。