FPGA的双口RAM能实现数据的累加和运算吗

时间:10-02

整理:3721RD

点击:

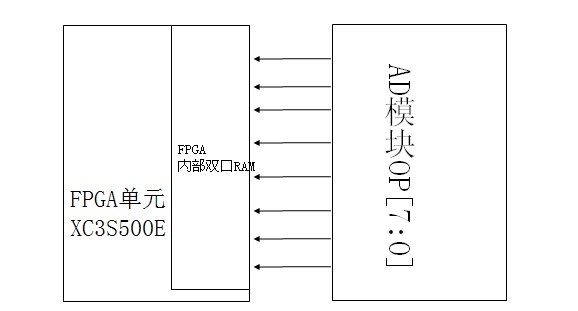

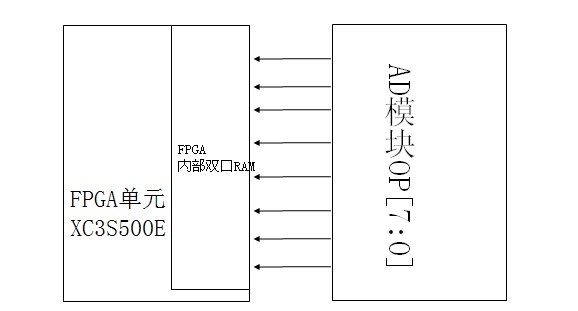

我的问题是这样的:从AD转化器通过OP[7:0]将每行128个数据传到FPGA的双口RAM进行数据缓存后发送给上位机,现在我想把每一行的第一个数据和下一行的第一个数据取平均(以此类推第一行的第二个数据和第二行的第二个数据......),请问能利用双口RAM实现吗 还说我需要先利用口RAM缓存前两行的数据 然后再相加去平均 我不知道我的描述是否清楚 网上找相关的资料实在是找不到啊

RAM不能,它只是存储数据,

你可以设置个数组,把前一行的数据缓存个里面,等第二行的数据过来时,与第一行里面的相加,然后向右移一位后存入RAM,在同时,将第二行的数据存到那个数组中(第一行的已经没用了),第第三行来的时候,再做同样的事情。

非常感谢 我去看看数组的编法~

学习。

调用系统的IP核就能轻易实现

能否说的再详细一点呢?不胜感激,我的FPGA用的是赛灵思的Spartan 3E系列

是只要相加后的数据吗?实现两行相加 只要缓存一行就可以了。整一个大于1行大小的FIFO,来的数据分成2路,一路进FIFO,一路寄存一下,到FIFO中存一行后,读FIFO数据和寄存器数据相加存入RAM就可以了

数据----->FIFO--------->

| +(FIFO计数>1行数据)--->RAM

--->D触发器寄存->

这个思路很受启发 我试着写写 非常感谢

那是应该用同步FIFO还是异步FIFO呢