RISC CPU 仿真图 怎样分析啊

时间:10-02

整理:3721RD

点击:

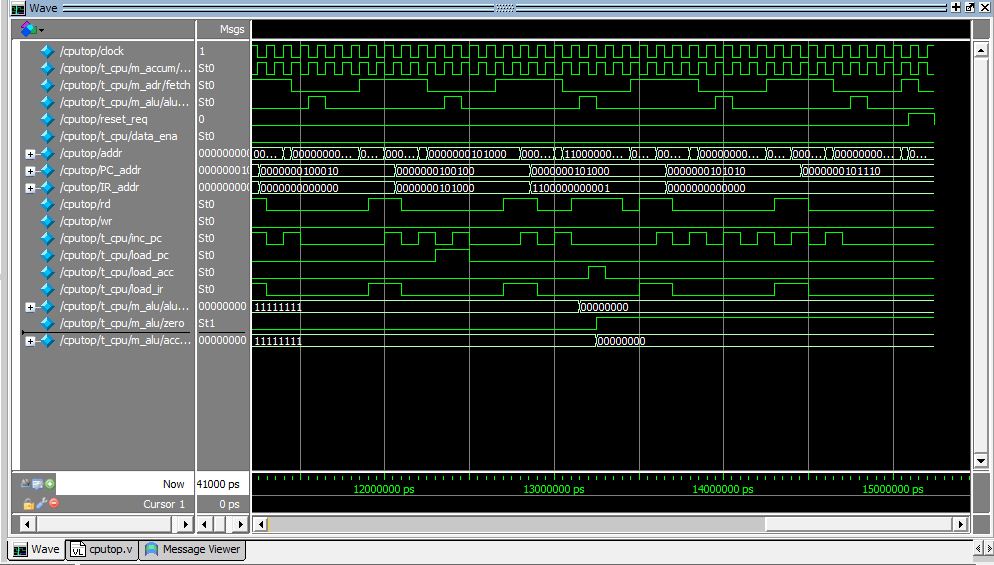

这是我得出的仿真图 怎样分析出一下结果:

1. RISC工作每执行一条指令需要八个时钟周期。RISC的复位和启动通过rst控制,rst高电平有效。Rst为低时,第一个fetch到达时CPU开始工作从Rom的000处开始读取指令,前三个周期用于读指令。

在对总线进行读取操作时,第3.5个周期处,存储器或端口地址就输出到地址总线上,第4--6个时钟周期,读信号rd有效,读取数据到总线,逻辑运算。第7个时钟周期,rd无效,第7.5个时钟地址输出PC地址,为下一个指令做好准备

对总线写操作时,在第3.5个时钟周期处,建立写的地址,第4个时钟周期输出数据,第5个时钟周期输出写信号。至第6个时钟结束,第7.5时钟地址输出PC地址,为下一个指令周期做好准备。

1. RISC工作每执行一条指令需要八个时钟周期。RISC的复位和启动通过rst控制,rst高电平有效。Rst为低时,第一个fetch到达时CPU开始工作从Rom的000处开始读取指令,前三个周期用于读指令。

在对总线进行读取操作时,第3.5个周期处,存储器或端口地址就输出到地址总线上,第4--6个时钟周期,读信号rd有效,读取数据到总线,逻辑运算。第7个时钟周期,rd无效,第7.5个时钟地址输出PC地址,为下一个指令做好准备

对总线写操作时,在第3.5个时钟周期处,建立写的地址,第4个时钟周期输出数据,第5个时钟周期输出写信号。至第6个时钟结束,第7.5时钟地址输出PC地址,为下一个指令周期做好准备。

讲的乱七八糟,先看看体系结构吧~

建议先看基础性的东西,理解了原理,再看实现就简单多了