ISE 如何实现8倍频

时间:10-02

整理:3721RD

点击:

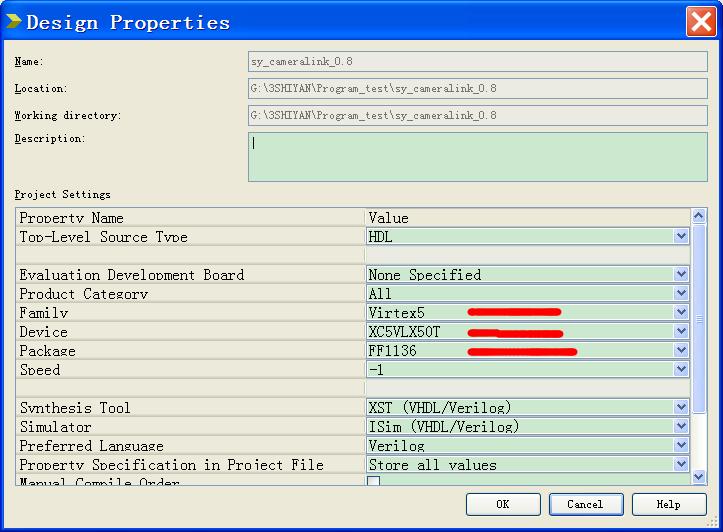

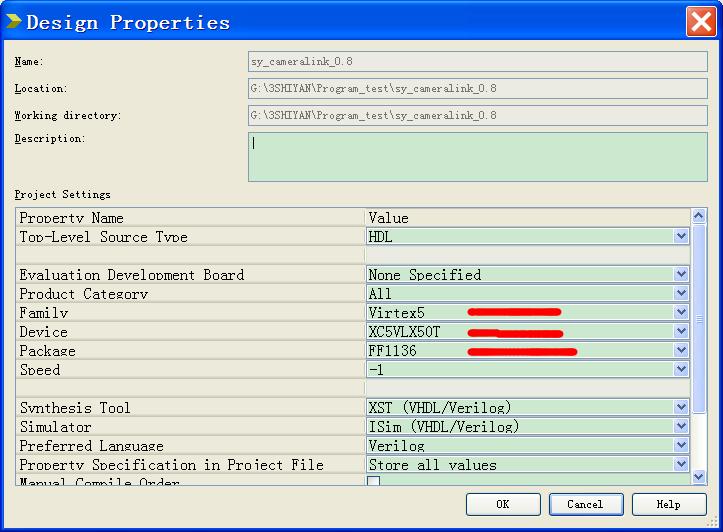

现在输入时钟为36.15MHz,想生成一个36.15*8=289.2Mhz的时钟,求教各路大神,ISE如何实现?

感觉很诡异啊,用ip核吧

7系以下的片子,可能具有三种原语,分别是DCM、PLL_BASE、PLL_ADV,有的只有DCM,有的三个都有,你随便用哪个做个2倍频就完了,但我不知道小数点分频的精度,这个手册上有公式算,你可以参考下xilinx 各个FPGA的user guide里面的clock source介绍,很清楚。

7系则是一般用MMCM这个东西来做时钟处理。

其实调个IPcore就完了,系数一添加就看得到生成的结果如何。

You can use the core generator to generate the ip with the PLL_ADV.

看你平台能否支持 不是想8就能8的

谢谢