用verilog写计数器

可以计时呀 不同电平的保持时间不同 然后由计时的信号计数

如2楼所说,先设置一个有使能的ns级计数器,当矩形波的上升沿一到来,就给计数器一个使能信号使其计时,然后当矩形波下降沿一到来,就关闭计数器,这样就明显了!

类似开关一样计数嘛

路过同求啊

路过,同问,在做课设

是只有1000ns和500ns宽度的高电平出现吗?

写个小程序,仅供参考一下

补充说明一下,仿真时clk为50MHz信号

- module counter(

- clk,

- signal,

- rst_n,

- o_signal//for test

- );

-

- input clk;

- input signal;

- input rst_n;

- //for test

- output o_signal;

- assign o_signal = signal;

- reg signal_reg;

- wire signal_wire;

- assign signal_wire = signal_reg;

- reg[7:0] count;

- reg[31:0] cnt_1;

- reg[31:0] cnt_2;

- always@(posedge clk or negedge rst_n)

- begin

- if (!rst_n)

- begin

- count <= 8'd0;

- cnt_1 <= 32'd0;

- cnt_2 <= 32'd0;

- end

- end

- always@(posedge clk)

- signal_reg <= signal;

- always@(posedge clk)

- begin

- if (signal_reg == 1)

- count <= count + 1'b1;

- else

- count <= 8'b0;

- end

- always@(negedge signal_wire)

- begin

- if ((count == 8'd50) && (!signal_wire))

- cnt_1 <= cnt_1 + 1'b1;

- else if ((count == 8'd25) && (!signal_wire))

- cnt_2 <= cnt_2 +1'b1;

- else ;

- end

- endmodule

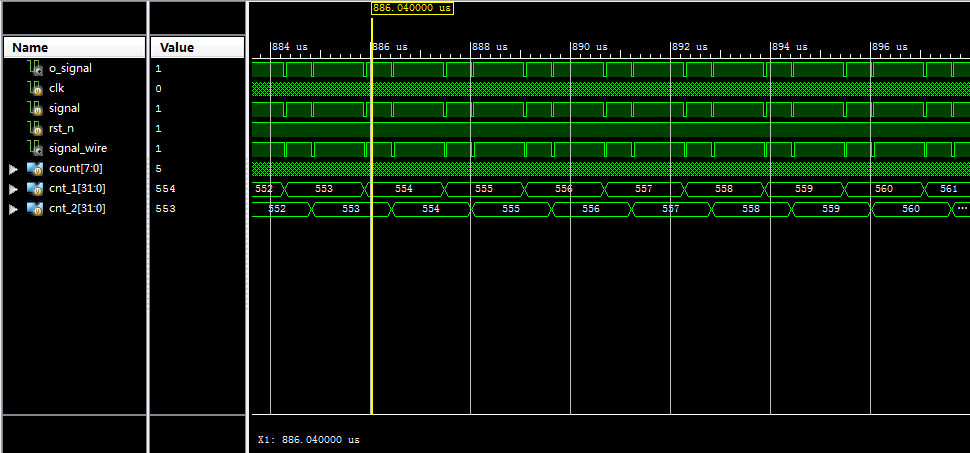

有仿真如下:

下面有个小程序,可以参考一下

45-52行是什么意思?

对两个不同宽度的高电平分别计数

我感觉,signal_wire刚刚从1变到0的那个下降沿,count会是任意值,跟signal_reg为1的时间长度有关,比如某次signal_reg持续为1的时间是100个clk周期,根据37-41行,count为100.假设然后signal信号从1变到0,45-52行激活,47行的if和49行的if else都不满足(此时count==100, !signal_wire==1, count不满足),cnt_1和cnt_2没有变化。

只要有足够快的时钟,这个问题应该很简单!

额,我忘记说了。补充一下,我仿真时用的clk为50MHz的,一个周期为20ns,可能没说清楚

You code has some mistake of the line from 45 to 52.The combination circuit can't use the none-blocking assignment.

I modify the code shows below.

- always@*

- begin

- if ((count == 8'd50) && (!signal_wire))

- cnt_1 = cnt_1 + 1'b1;

- else if ((count == 8'd25) && (!signal_wire))

- cnt_2 = cnt_2 +1'b1;

- end

谢谢,想请教一下为什么非阻塞赋值用在这里不合适呀?才自学Verilog一个月多点,有些细节可能掌握的不太好,给讲解下吧,谢谢。

You write the RTL code that has two concepts one is the combination circuit the other is the sequence circuit.The combination circuit are used the blocking assignment.

The sequence circuit are used the non-blocking assignment

niuren

谢谢了~

学习学习下