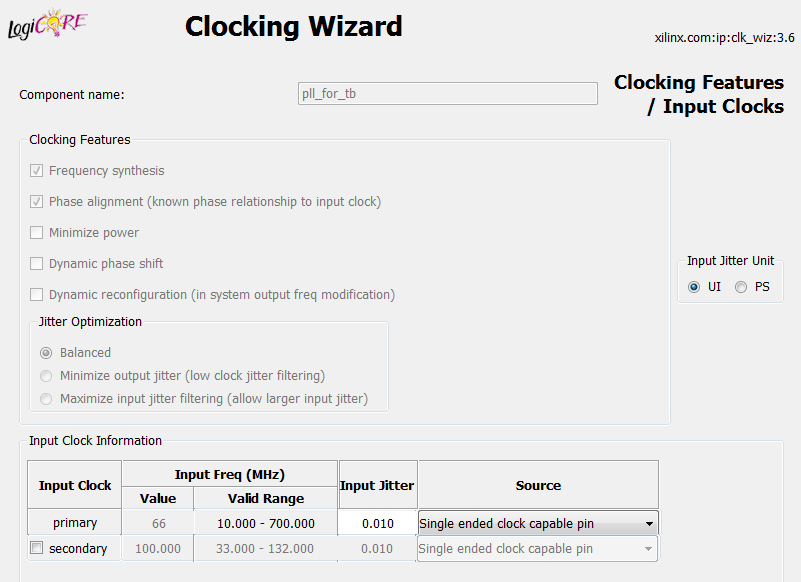

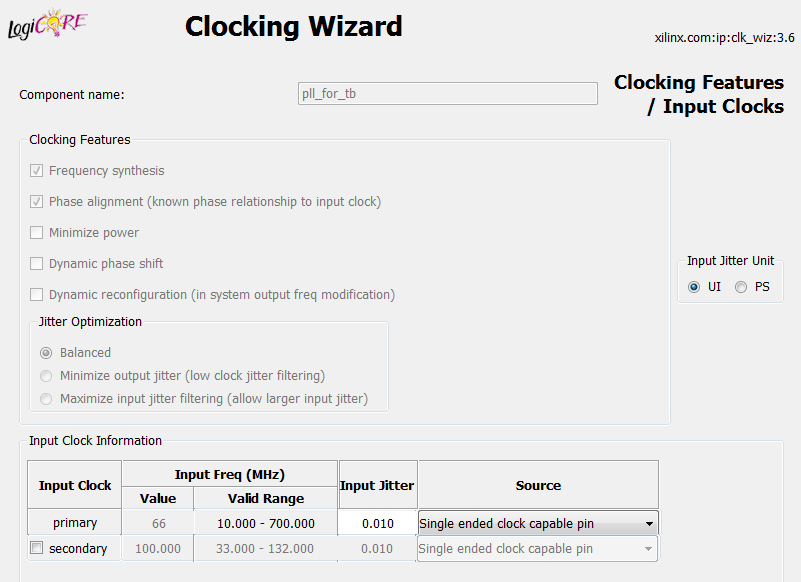

fpga 的clock wizard 输入时钟为什么是66M

时间:10-02

整理:3721RD

点击:

请教fpga 的clock wizard 输入时钟为什么是66M?片上晶振66M的么?

这个是我没有说清楚,这个PLL IP是用于生成电路所需的全部时钟,它的input clk 需要是 66MHz 外部的晶振频率吧

这是默认值,可以根据你实际用的来修改啊。

可以改?如果是外部晶振的固定频率,就不能改了吧?

virtex6

- Clocking

- 200 MHz Oscillator (Differential)

- 66 MHz Socketed Oscillator (Single-Ended)

- SMA Connectors for external clock (Differential)

- GTX Reference Clock port with 2 SMA connectors

这个是我没有说清楚,这个PLL IP是用于生成电路所需的全部时钟,它的input clk 需要是 66MHz 外部的晶振频率吧

问题是:

在ucf里面为何没有指定晶振pin的location,而是定义了频率66M?

NET "i_clk" TNM_NET = "i_clk";

TIMESPEC TS_i_clk = PERIOD "i_clk" 15.151 ns HIGH 50 %;

应该有location的,仔细找一下,如果没有,那要对比一下参考设计的工程或者文档了

学习学习