弱问I2C master读数据时,时钟是由谁产生的?

器件本身有时钟,总线SCK也当做数据处理,不过这个数据是作为接收SDA的时序依据

你自己看看IIC的IP core的代码就清楚了

I2C master is in charge of generating the clock. All clock devices can send data based on a smiple protocol.

圣诞快乐,呵,我看到协议了,只是有点不清楚,时钟总线SCK是双向的,对于交换总线的控制权的细节不是很清楚,slave如何知道master端release总线,slave何时把时钟总线拉低,何时释放总线,master何时重新拥有总线控制权?

同样的事情发生在SDA总线上,slave或master发出ACK相应的过程中,交换控制权的细节是怎么的?

圣诞快乐,呵,我看协议不是很清楚,时钟总线SCK是双向的,对于交换总线的控制权的细节不是很清楚,slave如何知道master端release总线,slave何时把时钟总线拉低,何时释放总线,master何时重新拥有总线控制权?

同样的事情发生在SDA总线上,slave或master发出ACK相应的过程中,交换控制权的细节是怎么的?

还有,slave是在SCK的上升沿采数的是么?麻烦啦?

Yes, or you can capture data at clock high period..

Please refer to I2C protocol about "Data validity".

恩,看过了,没有说的很明确,提到了data validity的范围。

还要请教一个multi master 的问题,如何避免在一个master传输数据过程中,另一个master启动,如何仲裁?

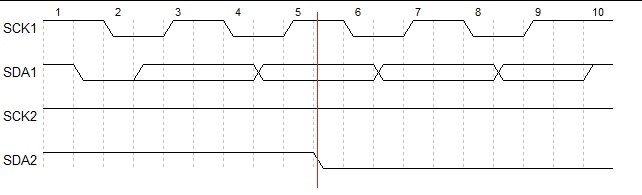

在上图的红线标记出,master2如何知道该总线是free状态还是busy状态,假如说SCK1和SDA1同时为1

哦啦啦了拉拉,我误入歧途了。

还有一个问题不是很清楚,multi-master在竞争的时候,如果竞争失败,那么数据就丢失了,丢了就丢了是吧?

IIC时钟由主机从机共同控制,但主要由主机控制,从机通过stretch功能拉低时钟,要求主机等待从机的内部操作

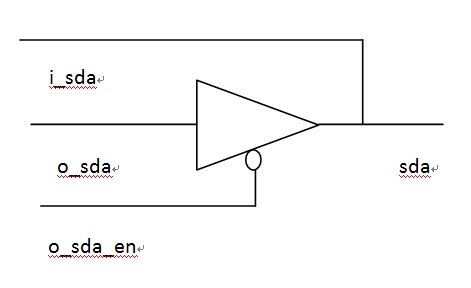

请教I2C的SDA三态门。enable端口可以 always 等于0么?

任何时候都是主机产生时钟

关注。