讨论一个代码问题,涉及前后端,验证

1:

always@(*) begin

if(a==1'b1 && b==1'b1 && c==1'b1)

out = 1'b1;

else

out = 1'b0;

end

2:

always@(*) begin

if(a==1'b0)

out = 1'b0;

else if(b==1'b0)

out = 1'b0;

else if(c==1'b0)

out = 1'b0;

else

out = 1'b1;

end

1和2在写法上有不同:

1的话条件多,很多时候不便于分析,当条件名字长和多时,要几行才能写下来时。

2的写法比较便于分析,但是代码行数多。

1在仿真时,条件覆盖率比较难。

2在仿真时,条件覆盖率不是问题。

1和2在逻辑级数上是一样的。

现在想讨论下

1:两个写法在仿真上是还有那些不同?比如那个更占资源?边界条件覆盖上有那些区别?

2:在synophsys的工具中哪一种写法支持比较好?DC?

3:1和2在逻辑实现上是否一致?或者那个更优?

4:大家更支持哪种写法?

看工具。代码检视优于技巧。面积不是绝对。

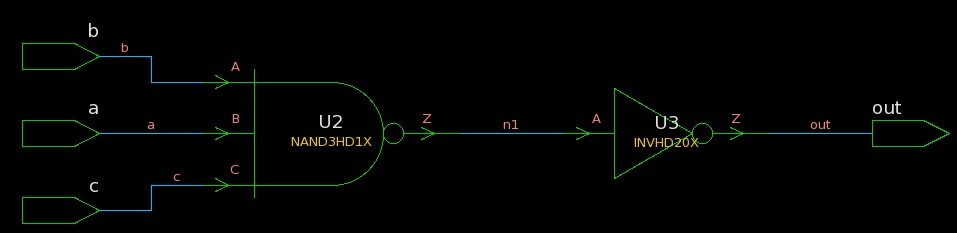

生成的电路结构不一样吧

呵呵,,大家继续看看

要是我的话会这样写

always@*

if ({a,b,c}==3'b111)

out =1'b1;

else

out=1'b0;

>>1的话条件多,很多时候不便于分析,当条件名字长和多时,要几行才能写下来时。

>>2的写法比较便于分析,但是代码行数多。

这个个人觉得未必。1完全可以写成if (a&b&c),就不长了。2如果if else嵌套得很多的话,分析也很累的。

>>1在仿真时,条件覆盖率比较难。

>>2在仿真时,条件覆盖率不是问题。

这个1和2应该是一样的,个人觉得。

>>1:两个写法在仿真上是还有那些不同?比如那个更占资源?边界条件覆盖上有那些区别?

>>2:在synophsys的工具中哪一种写法支持比较好?DC?

>>3:1和2在逻辑实现上是否一致?或者那个更优?

如果用dc+ compile_ultra的话,应该是完全一样的。

>>4:大家更支持哪种写法?

事实上我个人更支持assign out=a&b&c;

为了前后仿一致,尽量别用if else去表达组合逻辑。

大部分的时候,优化都靠综合器综合了

code的要求越来越低了,但逻辑性一定要对

综合下,发现两种写法的DC综合结果都是一样的。

电路结构完全一样。

同意6楼

工具蛮智能的。

如果是FPGA的话,综合出来的结果应该是一样的!因为才3个输入,用一个LUT就搞定了

综合出来的效果是一样的,至于语法我觉得形式上差别不大

我觉得不如直接写成assign out=a&b&c;这样更接近电路的实际情况。

感谢各位的热心回答,

在我司,要求组合逻辑用always搭,assign尽量不用来搭复杂逻辑。

在1种写法中条件覆盖率时比较难覆盖,2的话是用行覆盖率去处理的。

呵呵,我们很少用这种写法,公司要求显示表达所有信号

在做条件覆盖率时,1的确比较难覆盖。2基本没有问题。

我们公司不让用assign搭复杂逻辑。

我个人喜欢第二种,逻辑层次简单。

现在是以前项目建议用第二种写法,现在项目建议用第一种写法。

是的,从功能上是一致的,

只是想看看那个写法比较好

学习了 呵呵