Xilinx在线逻辑分析仪chipscope inserter 有两个输入时钟怎么办

等待高手来解答吧,菜鸟帮你顶贴一下……

谢谢啊,我自己也来顶下~

加频率比较高的那个时钟就可以了,chipscose看波形时有个时间刻度,这个刻度就是你的clock signal,也就是说每个刻度处,其实就是你clock signal的上升沿,再把那个频率较低的时钟加入trigger signal就行了

谢谢你的回答 ,但是我试了下没有数据哦,比如把一个数据流高频输入,低频输出,要是只有高频时钟输入,输出的时侯是不是也是由高频时钟触发了?

不是,其实你用哪个时钟做clock signal都无所谓,clock signal只是提供波形的刻度,不论你选哪个时钟作为clock signal,不会影响你的设计本身。你说没有输出,可能没有抓取到波形,设置一下触发条件就行。你的设计里有没有输出有效信号?有的话你把输出有效信号的触发条件设为1,再运行看波形

设置后一直这个状态,没有数据。

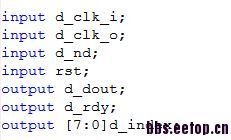

输入输出端口如下:

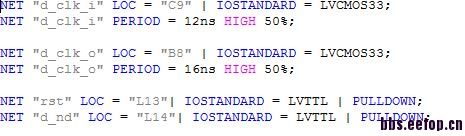

下面是输入端口约束;

我观察其他只有一个时钟输入的模块的时候都是对的,操作流程应该没有问题,不知道是哪里错了

你这是一个时钟用来写数据,一个时钟用来读数据吧,既然是多时钟域,有没有做同步处理?数据量多大,需不需要缓冲?

建议你用试试输入差分时钟,然后用分频的办法来得到两个工作时钟,ISE有分频的IP核可以调用,v6上是clocking wizard

数据不大,功能仿真是对的,那我试试输入一个时钟再分频吧。

你说的是DCM?我有一个时钟模块用DCM做分频,但是输入时钟选择external的时候,输入会先经过一个BUF,所以在chipscope 选择时钟信号的时候没有可用的输入时钟(没有clk_in_ibuf这个信号),而且占空比也不对,不知你知不知道什么原因。现在我在尝试用代码进行分频,不调用DCM。

功能仿真对并不代表时序对,下载到板子上最重要的是时序是否满足setup、hold,多时钟域尤其要小心设计。可以先做一下后仿

DCM没用过,我用的V6的片子,对应的时钟管理是Clock Wizard,配置时钟频率,占空比,相移什么的都很方便。分频出来的时钟就可以作为chipscope的clock signal啊。

学习学习咯

我用的是spartan 3E的板,ISE 13.1 clock wizard是会灰色的,不能用,话说用代码分频很麻烦呢,特别是小数没有锁相环不稳定

有用不?