紧急求助,Modelsim仿真时候遇到的奇怪问题,现象简单,但是没法解释

本人在仿真VHDL代码时,遇到了问题,希望高手解答啊!谢谢

以下时在仿真时候遇到的问题和现象,请耐心看完,如果您没有耐心,可以直接跳到最后的一段话和附图。

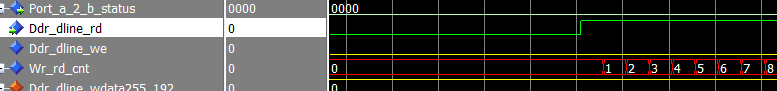

[attach]557741[/attach]

1. 粉色框所示,Wr_rd_cnt应该在Ddr_dline_cnt拉高一个cycle后才会+1,结果如图所示,在拉高的同时就已经+1了。这段程序如下:

Process(Rst,Clk)

begin

if Rst = '1' then

Wr_rd_cnt <= (Others=>'0');

elsif rising_edge(Clk) then

if State_start = '1' then

Wr_rd_cnt <= (Others=>'0');

elsif Ddr_dline_we = '1' or Ddr_dline_rd = '1' then

Wr_rd_cnt <= Wr_rd_cnt + 1;

end if;

end if;

end Process;

同样的在Ddr_dline_rd的驱动下,Wr_rd_cnt是没有问题的(见第二个小图)。

2. 蓝色框所示,Ddr_dline_data[ 63:0]应该在一个cycle以后赋给Ping_0_din_a,结果同样是没有延迟。代码如下,

Process(Rst,Clk)

begin

if Rst = '1' then

Ping_0_din_a <= (Others=>'0');

Ping_1_din_a <= (Others=>'0');

Ping_2_din_a <= (Others=>'0');

Ping_3_din_a <= (Others=>'0');

Pang_0_din_a <= (Others=>'0');

Pang_1_din_a <= (Others=>'0');

Pang_2_din_a <= (Others=>'0');

Pang_3_din_a <= (Others=>'0');

elsif rising_edge(Clk) then

if Ping_ram_en = '1' then

Ping_0_din_a <= Ddr_dline_wdata(63 downto 0);

Ping_1_din_a <= Ddr_dline_wdata(127 downto 64);

Ping_2_din_a <= Ddr_dline_wdata(191 downto 128);

Ping_3_din_a <= Ddr_dline_wdata(255 downto 192);

elsif Pang_ram_en = '1' then

Pang_0_din_a <= Ddr_dline_wdata(63 downto 0);

Pang_1_din_a <= Ddr_dline_wdata(127 downto 64);

Pang_2_din_a <= Ddr_dline_wdata(191 downto 128);

Pang_3_din_a <= Ddr_dline_wdata(255 downto 192);

else

Ping_0_din_a <= (Others=>'0');

Ping_1_din_a <= (Others=>'0');

Ping_2_din_a <= (Others=>'0');

Ping_3_din_a <= (Others=>'0');

Pang_0_din_a <= (Others=>'0');

Pang_1_din_a <= (Others=>'0');

Pang_2_din_a <= (Others=>'0');

Pang_3_din_a <= (Others=>'0');

end if;

end if;

end Process;

3. 而另一个信号Ping_1_we_a可以正确传递,比Ddr_dline_we延迟一个始终周期,如上图绿色框所示。代码如下。

Dpram_we

<= "0001" when (Ddr_dline_we = '1' and Range_write = '1' and Wr_rd_cnt(6 downto 5) = "00") else

"0010" when (Ddr_dline_we = '1' and Range_write = '1' and Wr_rd_cnt(6 downto 5) = "01") else

"0100" when (Ddr_dline_we = '1' and Range_write = '1' and Wr_rd_cnt(6 downto 5) = "10") else

"1000" when (Ddr_dline_we = '1' and Range_write = '1' and Wr_rd_cnt(6 downto 5) = "11") else

"1111" when (Ddr_dline_we = '1' and Azimuth_write = '1') else

"0000";

Process(Rst,Clk)

begin

if Rst = '1' then

Ping_0_we_a_i <= "0";

Ping_1_we_a_i <= "0";

Ping_2_we_a_i <= "0";

Ping_3_we_a_i <= "0";

Pang_0_we_a_i <= "0";

Pang_1_we_a_i <= "0";

Pang_2_we_a_i <= "0";

Pang_3_we_a_i <= "0";

elsif rising_edge(Clk) then

if Ping_ram_en = '1' then

Ping_0_we_a_i <= Dpram_we(0 downto 0);

Ping_1_we_a_i <= Dpram_we(1 downto 1);

Ping_2_we_a_i <= Dpram_we(2 downto 2);

Ping_3_we_a_i <= Dpram_we(3 downto 3);

elsif Pang_ram_en = '1' then

Pang_0_we_a_i <= Dpram_we(0 downto 0);

Pang_1_we_a_i <= Dpram_we(1 downto 1);

Pang_2_we_a_i <= Dpram_we(2 downto 2);

Pang_3_we_a_i <= Dpram_we(3 downto 3);

else

Ping_0_we_a_i <= "0";

Ping_1_we_a_i <= "0";

Ping_2_we_a_i <= "0";

Ping_3_we_a_i <= "0";

Pang_0_we_a_i <= "0";

Pang_1_we_a_i <= "0";

Pang_2_we_a_i <= "0";

Pang_3_we_a_i <= "0";

end if;

end if;

end Process;

Ping_0_we_a <= Ping_0_we_a_i;

4. 其中的Ddr_dline_we和Ddr_dline_data[ 255:0]为模块端口输入,信号由另一个模块中通过读Fifo的数据产生。

具体程序见附件RAM_CTRL_PORT_A.vhd和RD_DDR.vhd。两个模块各自仿真时没有错误,夹杂别的模块一起仿真时候就会产生错误,并且每次都是这个位置。驱动时钟也是同一个。

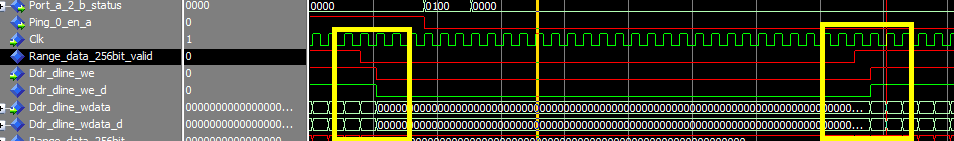

5. 我在RAM_CTRL_PORT_A.vhd中将输入信号Ddr_dline_we和Ddr_dline_wdata用时钟打了一拍,仿真出来结果却没有相应的延迟一个Cycle,Ddr_dline_we和Ddr_dline_we_d完全一致,Ddr_dline_wdata和Ddr_dline_wdata_d也完全一致。

回应第一个问题:“Wr_rd_cnt应该在Ddr_dline_we拉高一个cycle后才会+1“ 你这个认识好像不对吧。在Ddr_dline_we拉高后的第一个时钟上升沿,Wr_rd_cnt+1,而不一定是一个cycle。由图可见,你的Ddr_dline_we和Wr_rd_cnt应该不是同一个时钟域。建议你把信号Ddr_dline_we用这个时钟打一拍,然后再用同一个时钟域的信号。

没有看懂,呵呵。