综合后电路与前仿波形不一致的情况,请大家进来分析分析!

时间:10-02

整理:3721RD

点击:

小弟最近写一个模块的时序,遇到了综合后电路与前仿波形不一致的情况,大概如下:代码是:

- always@(WRITE_Counter[10:7])

- case(WRITE_Counter[10:7])

- 4'b0000: Write_Comm<={Ram0_Data,Ram0_Addr};

- 4'b0001: Write_Comm<={Ram1_Data,Ram1_Addr};

- 4'b0010: Write_Comm<={Ram2_Data,Ram2_Addr};

- 4'b0011: Write_Comm<={Ram3_Data,Ram3_Addr};

- 4'b0100: Write_Comm<={Ram4_Data,Ram4_Addr};

- 4'b0101: Write_Comm<={Ram5_Data,Ram5_Addr};

- 4'b0110: Write_Comm<={Ram6_Data,Ram6_Addr};

- 4'b0111: Write_Comm<={Ram7_Data,Ram7_Addr};

- // 4'b1000: Write_Comm<={Status_Data,Status_Addr};

- default:Write_Comm<=32'h0000_0000;

- endcase

- always@(WRITE_Counter[6:1])

- case(WRITE_Counter[6:1])

- 6'b000_000:Write_Seri<=Write_Comm[0];

- 6'b000_001:Write_Seri<=Write_Comm[1];

- 6'b000_010:Write_Seri<=Write_Comm[2];

- 6'b000_011:Write_Seri<=Write_Comm[3];

- 6'b000_100:Write_Seri<=Write_Comm[4];

- 6'b000_101:Write_Seri<=Write_Comm[5];

- 6'b000_110:Write_Seri<=Write_Comm[6];

- 6'b000_111:Write_Seri<=Write_Comm[7];

- 6'b001_000:Write_Seri<=Write_Comm[8];

- 6'b001_001:Write_Seri<=Write_Comm[9];

- 6'b001_010:Write_Seri<=Write_Comm[10];

- 6'b001_011:Write_Seri<=Write_Comm[11];

- 6'b001_100:Write_Seri<=Write_Comm[12];

- 6'b001_101:Write_Seri<=Write_Comm[13];

- 6'b001_110:Write_Seri<=Write_Comm[14];

- 6'b001_111:Write_Seri<=Write_Comm[15];

- 6'b010_000:Write_Seri<=Write_Comm[16];

- 6'b010_001:Write_Seri<=Write_Comm[17];

- 6'b010_010:Write_Seri<=Write_Comm[18];

- 6'b010_011:Write_Seri<=Write_Comm[19];

- 6'b010_100:Write_Seri<=Write_Comm[20];

- 6'b010_101:Write_Seri<=Write_Comm[21];

- 6'b010_110:Write_Seri<=Write_Comm[22];

- 6'b010_111:Write_Seri<=Write_Comm[23];

- 6'b011_000:Write_Seri<=Write_Comm[24];

- 6'b011_001:Write_Seri<=Write_Comm[25];

- 6'b011_010:Write_Seri<=Write_Comm[26];

- 6'b011_011:Write_Seri<=Write_Comm[27];

- 6'b011_100:Write_Seri<=Write_Comm[28];

- 6'b011_101:Write_Seri<=Write_Comm[29];

- 6'b011_110:Write_Seri<=Write_Comm[30];

- 6'b011_111:Write_Seri<=Write_Comm[31];

- default:Write_Seri<=1'b0;

- endcase

- assign SPI_MOSI =Write_Seri ;

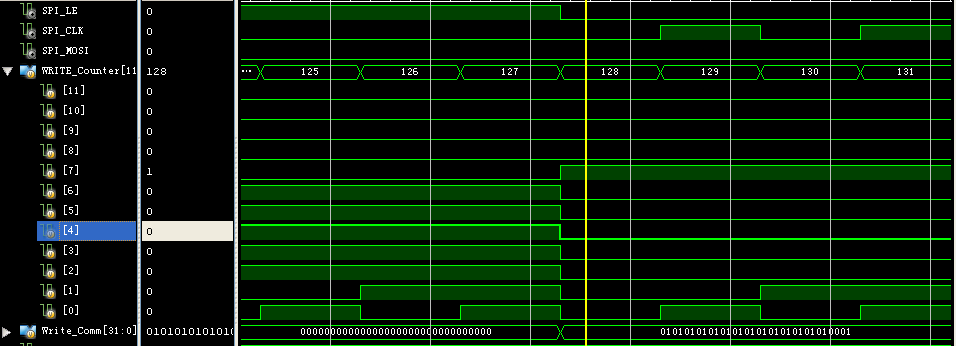

仿真波形如下图:

这段代码应该是综合成两个数据选择器,但为什么计数器计到128时(WRITE_Counter[10:7]变为001),Write_Comm数值变化了,Write_Seri却没有做相应变化。求大家帮帮我。如何做到仿真与电路功能完全一致呢?

在第二个always中 Write_Comm是作为输入,是不是应该放入到always的敏感列表中呢

恩 应该都要放进去的

敏感列表没写全。

其实第二个case语句只要一句话assign Write_Seri=rite_comm[WRITE_Counter[6:1]];就行了。

恩,综合出来的电路一样吗?

敏感列表沒寫全,第一個和第二個always都是。

最好还是加时钟,用时序逻辑吧

为什么用时序逻辑?时序逻辑面积大,功耗高,速度慢啊!

当然一样

comn 放到第2个always 敏感变量列表中

2001语法支持 always(*) 更方便

支持10楼的观点

恩 我知道了。但是我觉得还是自己写比较好