循环路径的时序约束

最近在学synopsys DC做了一个设计 工作周期 5ns

input_delay 1.5ns

report_timing slack都为正

但是为什么vcs仿真dc输出的网表文件testbench周期要设置为20ns以上结果才正确呢

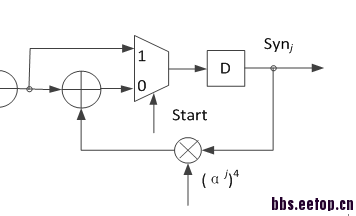

图中左端为数据输入端 设计中有一部分逻辑是D触发器里面的数据经过更新在下一个时钟周期重新输入同一个D触发器 想问一下这样的路径要专门约束吗 仅仅设置一个input_delay 能对这样的循环路径产生约束吗 如果不用的话为什么dc clock_period设为5ns slack都为正 但是用vcs dve仿真dc的输出网表的时候却无法输出正确波形呢 而将testbench里面的周期调大是可以输出正确波形的 说明电路结构应该没问题 而是路径延时的问题 到底什么情况呢 头大啊

门仿是否读了反标文件?

打开sdf文件看看里面的delay是否正确

反标文件是什么啊 小白不懂 门仿是用dc综合得到的门级网表+ testbench+对应的tsmc的库仿的

是write_sdf得到的文件吗 (DELAYFILE

(SDFVERSION "OVI 2.1")

(DESIGN "bchDec_syn")

(DATE "Thu Mar 28 10:30:36 2013")

(VENDOR "slow")

(PROGRAM "Synopsys Design Compiler cmos")

(VERSION "D-2010.03")

(divIDER /)

(VOLTAGE 1.62:1.62:1.62)

(PROCESS "slow")

(TEMPERATURE 125.00:125.00:125.00)

(TIMESCALE 1ns)

(CELL

(CELLTYPE "bchDec_syn")

(INSTANCE)

(DELAY

(ABSOLUTE

(INTERCONNECT U957/Y U1211/A (0.000:0.000:0.000))

(INTERCONNECT U1206/Y U1207/A (0.000:0.000:0.000))

(INTERCONNECT U1172/Y U1207/B (0.000:0.000:0.000))

(INTERCONNECT U932/Y U1206/A (0.000:0.000:0.000))

(INTERCONNECT U1134/Y U1206/B (0.000:0.000:0.000))

(INTERCONNECT U1185/Y U1186/A (0.000:0.000:0.000))

(INTERCONNECT synTemp5_reg_7_/Q U1185/A (0.000:0.000:0.000))

(INTERCONNECT U812/Y U1184/A (0.000:0.000:0.000))

(INTERCONNECT U918/Y U1172/A (0.000:0.000:0.000))

(INTERCONNECT U815/Y U1171/A (0.000:0.000:0.000))

(INTERCONNECT m5_4/U2/Y U1123/A (0.000:0.000:0.000))

(INTERCONNECT U812/Y U1118/A (0.000:0.000:0.000))

(INTERCONNECT U937/Y U1117/A0 (0.000:0.000:0.000))

(INTERCONNECT U1118/Y U1117/A1 (0.000:0.000:0.000))

(INTERCONNECT U1221/Y U1117/B0 (0.000:0.000:0.000))

(INTERCONNECT U822/Y U1117/B1 (0.000:0.000:0.000))

(INTERCONNECT synTemp5_reg_4_/Q U1116/A (0.000:0.000:0.000))

(INTERCONNECT U805/Y U1115/A (0.000:0.000:0.000))

(INTERCONNECT U1104/Y U1114/A (0.000:0.000:0.000))

(INTERCONNECT syn2_reg_6_/Q U1104/A (0.000:0.000:0.000))

(INTERCONNECT U930/Y U1098/A0 (0.000:0.000:0.000))

(INTERCONNECT U931/Y U1098/A1 (0.000:0.000:0.000))

(INTERCONNECT U1306/Y U1098/B0 (0.000:0.000:0.000))

(CELL

(CELLTYPE "XOR2X1")

(INSTANCE m5_4/U19)

(DELAY

(ABSOLUTE

(COND B == 1'b1 (IOPATH A Y (0.408:0.408:0.408) (0.365:0.365:0.365)))

(COND B == 1'b0 (IOPATH A Y (0.332:0.332:0.332) (0.287:0.287:0.287)))

(IOPATH (posedge A) Y (0.445:0.445:0.445) (0.365:0.365:0.365))

(IOPATH (negedge A) Y (0.408:0.408:0.408) (0.342:0.342:0.342))

(COND A == 1'b1 (IOPATH B Y (0.479:0.480:0.480) (0.421:0.421:0.421)))

(COND A == 1'b0 (IOPATH B Y (0.397:0.397:0.397) (0.396:0.398:0.398)))

(IOPATH (posedge B) Y (0.600:0.600:0.600) (0.543:0.543:0.543))

(IOPATH (negedge B) Y (0.479:0.480:0.480) (0.410:0.411:0.411))

)

)

)

(CELL

(CELLTYPE "XOR2X1")

(INSTANCE m5_4/U18)

(DELAY

(ABSOLUTE

(COND B == 1'b1 (IOPATH A Y (0.500:0.500:0.500) (0.406:0.406:0.406)))

(COND B == 1'b0 (IOPATH A Y (0.396:0.396:0.396) (0.350:0.350:0.350)))

(IOPATH (posedge A) Y (0.509:0.509:0.509) (0.406:0.406:0.406))

(IOPATH (negedge A) Y (0.500:0.500:0.500) (0.401:0.401:0.401))

(COND A == 1'b1 (IOPATH B Y (0.494:0.494:0.494) (0.433:0.433:0.433)))

(COND A == 1'b0 (IOPATH B Y (0.399:0.399:0.399) (0.375:0.375:0.375)))

(IOPATH (posedge B) Y (0.505:0.505:0.505) (0.434:0.434:0.434))

(IOPATH (negedge B) Y (0.494:0.494:0.494) (0.430:0.430:0.430))

)

)

)

这玩意怎么看啊

而且综合完的网表和原始设计怎么对应起来啊

比如我想看一下a[9:0]^b[9:0]综合成的网表要怎么找到对应的电路结构啊

在仿真的时候,读取sdf文件。我之前遇到门仿库文件中定义的延时值过大,导致门仿不能通过的情况,所以建议你读sdf文件。

initial $sdf_annotate ("sdf_file path", instantiation name, "MAXIMUM");

好像是没有读取sdf文件,sdf文件怎么读取,是在testbench?网表?还是启动命令行?那一句命令没太看懂

$sdf_annotate命令加到testbench里面。

按你的方法在testbench里面加了 initial $sdf_annotate("./bchDec_Top.sdf",bchDec_Top);语句 “maximum”报错 我也不知道什么意思 所以去掉了 然后vcs 有error:SDF Error: Negative HOLD value replaced by 0. Add +neg_tchk to consider Negative delay value.加上+neg_tchk后没有error了 另外还有warning:SDF Warning: IOPATH from A to Y is not found.(很多)没管,然后dve看波形 仿真周期设为5ns 波形没问题了 非常感谢 还有一点疑问就是+neg_tchk这条语句为什么error就没了呢 是问题解决了吗 不是有Negative HOLD value (hold slack为正,为什么会有Negative HOLD value呢),另外IOPATH from A to Y is not found这样的warning需要去管吗?

1. 时序里面存在best, typical和worst三种情况,所以SDF里面也可以将三种情况分别写出来. maximum参数告诉工具读取SDF文件中的哪一类参数。

2.+neg_tchk和path not found的问题,我也不太清楚。

好的 谢谢

把“maximum” 换成 "worst" 后还会报错吗

也不行 Warning-[SDFCOM_CNOF] Cannot Open File

SDF Config Error: Cannot open sdf config file worst for reading.

No such file or directory.

我的sdf是dc生成的 没有什么typical best和worst区分 不知道用Pt生成的行不行 或者有可能我的库只用了slow.db的原因

maximum前面要3个逗号吧

你从D的输出回到D的输入的这段路径上的延时比较小,导致hold time 有violation。提示你加neg_tcheck其实是让工具不再检查这类的violation,也就是说,碰到这种情况也不会报错,所以error不见了。pre_sim时常常会在一些电路加上tcheck以避开时序检查。