计数器的代码不能被综合

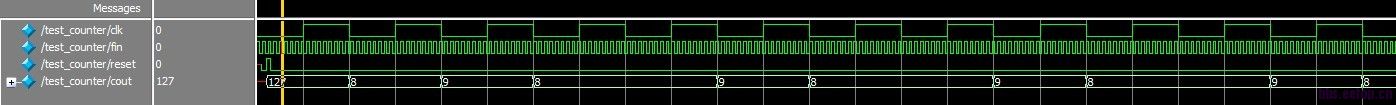

用verilog写了个计数器的代码,异步复位,clk的高电平期间对fin计数,clk的下降沿输出计数值,modelsim里面做功能仿真没啥问题,但是DC综合的话就不行,报cout[6:0]和counter_buf[6:0]被多个源驱动,但是我查不出错误在哪儿,请教各位帮忙看看

- //Verilog HDL for "pll_system_sim", "COUNTER_AFC" "verilog"

- module COUNTER_AFC(clk,fin,reset,cout);

- input clk,fin,reset;

- output [6:0]cout;

- reg [6:0]cout;

- reg [6:0]counter_buf;

-

- always @(posedge reset or posedge fin)

- if (reset)

- begin

- counter_buf[6:0] <= 7'b0000000;

- cout[6:0] <= 7'b1111111;

- end

- else if (clk)

- counter_buf[6:0] <= counter_buf[6:0] + 1;

- always @(negedge clk)

- if (!reset)

- begin

- cout[6:0] <= counter_buf[6:0];

- counter_buf[6:0] <= 7'b0000000;

- end

- endmodule

错误比较多

reg只能在一个always块里赋值,你用了2个

15行中的clk怎么做为使能信号?

建议把时序图先画出来再理解透彻了再写代码吧。

看得比较乱

一个寄存器不能在2个always块里赋值,而且一般同步时序设计里面把clk信号用作时钟而非使能。

一般clk的频率要远大于fin的频率,感觉你对计数器电路的实现原理没弄透,做这个设计不像C语言,还是要看硬件时序的。

我这个计数器是对fin计数,fin的频率远高于clk,clk上升沿开始对fin计数,计数方式是采集fin的上升沿,clk下降沿计数结束并输出结果,如果没有异步复位倒也不难弄,有这个异步复位就不知道怎么弄了。本人是搞模拟的,数字方面接触不多。

这个电路的电路图应该是怎样的呢?

画一下你就知道为什么了。

1、使用fin得到clk的沿

2、上升沿计数。 不知道你的下降沿是否清0

3、下降沿输出

不太明白你的意思

clk下降沿输出计数值并保持到下一个下降沿来临之前,cout不用清零,但counter_buf要清零的

就这点东西,function能对才怪呢。回家好好看看书,基础的东西自己多学习

1、使用fin得到clk的沿,不知道同步异步的关系,假定为同步

2、下降沿输出

always @(posedge fin or posedge reset)

if(reset)

clk_d1 <= 1'b0;

else

clk_d1 <= clk;

assign clk_negedge = clk_d1==1'b1 && clk==1'b0;

always @(posedge fin or posedge reset)

if(reset)

counter_buffer <= 7'b0;

else (clk) //饱和翻转

counter_buffer <= counter_buffer + 1;

else

counter_buffer <= 7'b0

always @(posedge fin or posedge reset)

if(reset)

counter <= 7'b0;

else if(clk_negedge)

counter <= counter_buffer;

另外,fin不是时钟的话怎么能写到敏感列表里?这是绝对错误的。

小编这个很给力,特别是下降沿的判断……

呵呵,做射频的哥们来写代码了!求一点AFC资料啊!

比较乱,还是学习了