一个很弱的问题,关于D触发器

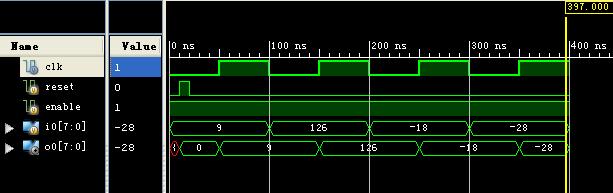

仿真结果如图:

当然这个模块的输出在后面还要被使用。 有一个问题就是:比如在这个仿真图中,第一个时钟上升沿之后输出就已经是9了。

那在后面的模块中,我能在第一个时钟上升沿之后就能使用这个9呢?还是至少得等到第二个时钟上升沿之后才能用啊?

因为助教一直跟我强调我不能在第一个周期使用这个9,至少要等到第二个周期,我对这个没懂。

希望知道的大侠们能帮帮我啊

助教说的是对的,因为触发器之后有一定的延迟,第一个clock是采不到你要的这个数据9的

学习了,,,

二楼说的有道理,建议你在写D触发器的时候加一个延时,这样在仿真的时候就比较容易理解。例如:

always @(posedge clk or posedge rst)

if(rst) out <= 0;

else out <= #1 in;

第二个沿才能够采到那个“9”。仿真没有像楼上加上一个延迟(#1),最好还是加上。如果不加,可以这样:沿前低电平对应时钟沿到来的D输入值,沿后的高电平对应时钟沿到达之后的Q输出值。

从电路结构上来说,该触发器在CLK低电平将数据打入到触发器内,然后再CLK变为高电平后输出打入的数据。可以认为是高电平触发、高电平复位的D触发器。而实际使用时,我在做工程的时候,是可以在第一个时钟上升沿后使用“9”。但是要注意,是否满足HOLD TIME。

贊成用

always @(posedge clk or posedge rst)

if(rst) out <= 0;

else out <= #1 in;

由於DELAY在合成時會被忽略掉

所以並不會對實際電路造成影響

但卻可幫助simulation時的除錯

reset最好长点,跨一两个cycle比较好

谢谢楼上各位的回答,受益了

还是6楼说的有道理

第一个时钟周期采数据的话建立时间肯定不足

第一个时钟周期采数据的话建立时间肯定不足

好像只有6楼的说的有道理!

同学习。

学习一下!

说的不错,学习了。最近也在郁闷怎么对输出采样!

觉得6楼把问题搞得复杂了,有些概念还混淆了。个人观点因为,对于D触发器,输入时外部信号,虽然恰好看到仿真波形是在时钟低电平时变化,但不能支持触发器低电平打入数据的结论。

由于触发器是时钟边沿触发,那么只有两种,要么是上升沿,要么是下降沿,从仿真波形看出,此触发器是上升沿触发。

小编提出的问题,助教的说法完全正确。

仿真时不必加延时,习惯就好。

个人觉得在时钟的下降沿使用采到的数据更合理