请教 MODELSIM 仿真正弦函数问题

时间:10-02

整理:3721RD

点击:

MATLAB产生的sin.txt文件放到工程目录下了啊。

程序:

module sin(clk,rst,y);

input clk;

input rst;

output y;

reg i;

reg data_out;

reg [7:0] data_mem[0:255]; //定义一个8bit X 256的数组

initial

$readmemh("sin.txt",data_mem); //将sin.txt中的数据读入存储器data_mem

always @(posedge clk)

begin

if(!rst)

begin

data_out <= 8'd0;

i <= 8'd0;

end

else

begin

data_out<=data_mem; //将存储器中的数据输出

i<=i+8'd1;

end

end

assign y=data_out;

endmodule

TESTBENCH:

`timescale 1ns/10ps

`include "sin.v"

module sin_test_testbench;

reg clk;

reg rst;

wire [255:0]y;

initial

begin

rst=0;

clk=0;

#1000 rst=1;

end

always

#50 clk=~clk;

sin i1(

.clk(clk),

.rst(rst),

.y(y)

);

initial begin

# 60000 $finish;

end

endmodule

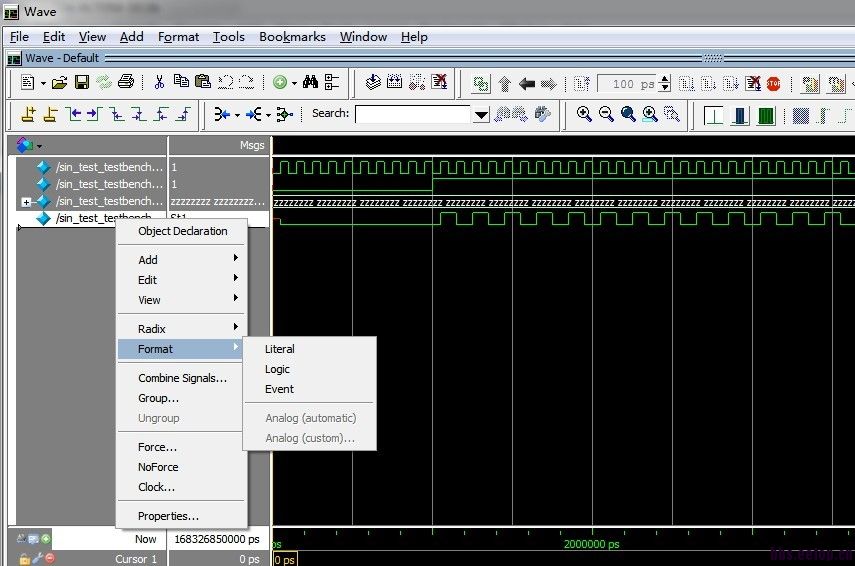

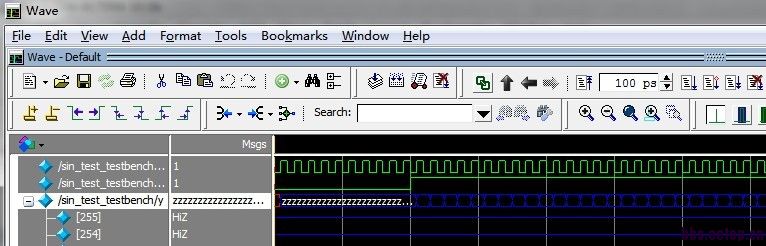

新手啊,编译时没有问题的,仿真图像怎么是这样的啊?

同学 右键把格式设为analog吧~

刚接触verilog,memory也不太懂,我想问一下,LZ在取memory值得时候 【 data_out<=data_mem; //将存储器中的数据输出 】 为什么没给memory加个地址,如 data_mem[i] ?

程序里面是有的,但是这个在帖子里面 中括号里面i 显示不出来,不知道怎么回事。还能看到另外的问题吗?