请问scan enable和scan clock在clock gating上不能正确连接应该如何处理?

时间:10-02

整理:3721RD

点击:

向大家请教一个问题,是关于scan enable和scan clock在clock gating上不能正确连接上的。具体情况是这样:

在综合core一层时插入了clock gating。

再对core netlist插scan, 这个netlist中包含clk_gen模块,core有两个时钟输入port,分别是ck_in和ck_system,ck_in是scan clock, ck_system是功能模式下的clock, 这两个时钟输入ck_gen模块,输出时钟是系统中各模块所需时钟,如ck_gpio, ck_usb等,在这个模块内部对这些生成的时钟用test_mode对ck_in和ck_system进行了mux。

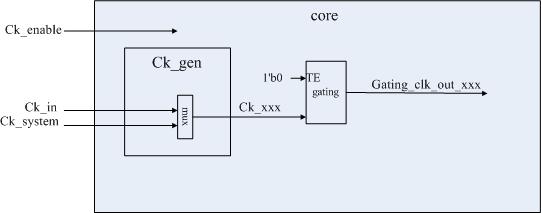

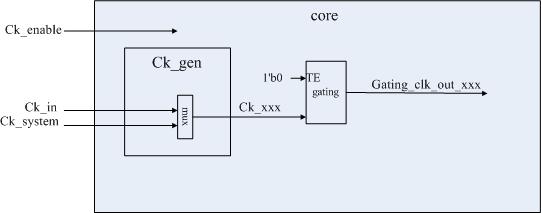

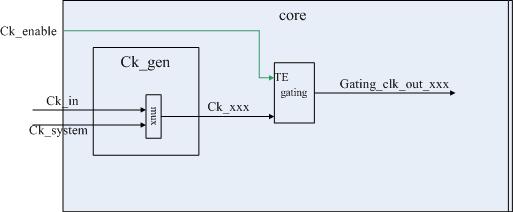

在未插scan时,综合出的core的netlist中各gating的TE端接的是1'b0, clk输入端接的是ck_gen输出的对应各子模块时钟,是正确的。

如下图1:

在插scan时脚本中指定ScanClock为core的ck_in port,ScanEnable为core的scan_enable port。

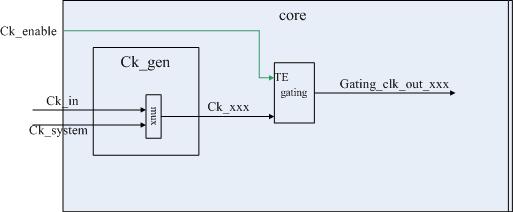

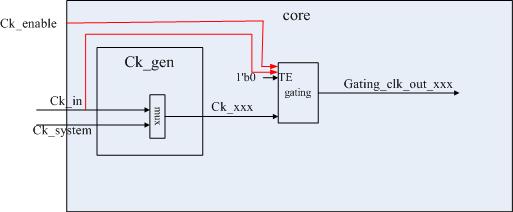

期望插完scan后的样子是clock gating不的clk输入端不变,同时TE端接到core的scan_enable port上。

如下图:

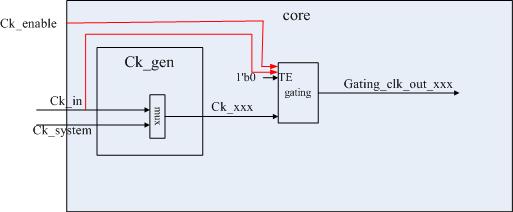

插完scan的netlist中出现了两个问题:

1.各clock gating新增了一个clk输入端口,接到core的ck_in port上。

2.各clock gating新增了一个TE端,接到core的scan_enable port上。而原来的TE仍接1'b0

如下图:

那么我该怎样才能把gating插成第二张图的形式呢?(用DC2009或DC2010)

谢谢!

在综合core一层时插入了clock gating。

再对core netlist插scan, 这个netlist中包含clk_gen模块,core有两个时钟输入port,分别是ck_in和ck_system,ck_in是scan clock, ck_system是功能模式下的clock, 这两个时钟输入ck_gen模块,输出时钟是系统中各模块所需时钟,如ck_gpio, ck_usb等,在这个模块内部对这些生成的时钟用test_mode对ck_in和ck_system进行了mux。

在未插scan时,综合出的core的netlist中各gating的TE端接的是1'b0, clk输入端接的是ck_gen输出的对应各子模块时钟,是正确的。

如下图1:

在插scan时脚本中指定ScanClock为core的ck_in port,ScanEnable为core的scan_enable port。

期望插完scan后的样子是clock gating不的clk输入端不变,同时TE端接到core的scan_enable port上。

如下图:

插完scan的netlist中出现了两个问题:

1.各clock gating新增了一个clk输入端口,接到core的ck_in port上。

2.各clock gating新增了一个TE端,接到core的scan_enable port上。而原来的TE仍接1'b0

如下图:

那么我该怎样才能把gating插成第二张图的形式呢?(用DC2009或DC2010)

谢谢!

这么仔细画的图居然没人回答,我顶!

SE直接hook up过去不行吗

1:什么工具?

2:gating cell用的什么?

感觉是需要hook up过去。

问另外一个问题,如何将有TE端clock gating cell变成不带TE端的,因为不是每个模块都期望加入scan chain的。

gating cell怎么没有EN端呢?

学习了