FPGA问题(这题目)

时间:10-02

整理:3721RD

点击:

先贴代码

input clk100m,

input sys_rst,

input [31:0]inter_in_max,

input [31:0]inter_in_min,

input [31:0]inter_in_sample,

input [31:0]inter_in_normal,

input data_en,

input inter_en,

input [3:0]inter_num,

mix inter_max (

.clk100m(clk100m),

.sys_rst(sys_rst),

.data_in(inter_in_max),

.data_en(data_en),

.inter_en(inter_en),

.inter_num(inter_num),

.data_out(inter_out_max_reg),

.data_out_en(inter_out_en_max)

);

mix inter_min (

.clk100m(clk100m),

.sys_rst(sys_rst),

.data_in(inter_in_min),

.data_en(data_en),

.inter_en(inter_en),

.inter_num(inter_num),

.data_out(inter_out_min_reg),

.data_out_en(inter_out_en_min)

);

mix inter_sample (

.clk100m(clk100m),

.sys_rst(sys_rst),

.data_in(inter_in_sample),

.data_en(data_en),

.inter_en(inter_en),

.inter_num(inter_num),

.data_out(inter_out_sample_reg),

.data_out_en(inter_out_en_sample)

);

mix inter_normal (

.clk100m(clk100m),

.sys_rst(sys_rst),

.data_in(inter_in_normal),

.data_en(data_en),

.inter_en(inter_en),

.inter_num(inter_num),

.data_out(inter_out_normal_reg),

.data_out_en(inter_out_en_normal)

);

这四个模块除了数据不一样。其他都一样吧。

input clk100m,

input sys_rst,

input [31:0]inter_in_max,

input [31:0]inter_in_min,

input [31:0]inter_in_sample,

input [31:0]inter_in_normal,

input data_en,

input inter_en,

input [3:0]inter_num,

mix inter_max (

.clk100m(clk100m),

.sys_rst(sys_rst),

.data_in(inter_in_max),

.data_en(data_en),

.inter_en(inter_en),

.inter_num(inter_num),

.data_out(inter_out_max_reg),

.data_out_en(inter_out_en_max)

);

mix inter_min (

.clk100m(clk100m),

.sys_rst(sys_rst),

.data_in(inter_in_min),

.data_en(data_en),

.inter_en(inter_en),

.inter_num(inter_num),

.data_out(inter_out_min_reg),

.data_out_en(inter_out_en_min)

);

mix inter_sample (

.clk100m(clk100m),

.sys_rst(sys_rst),

.data_in(inter_in_sample),

.data_en(data_en),

.inter_en(inter_en),

.inter_num(inter_num),

.data_out(inter_out_sample_reg),

.data_out_en(inter_out_en_sample)

);

mix inter_normal (

.clk100m(clk100m),

.sys_rst(sys_rst),

.data_in(inter_in_normal),

.data_en(data_en),

.inter_en(inter_en),

.inter_num(inter_num),

.data_out(inter_out_normal_reg),

.data_out_en(inter_out_en_normal)

);

这四个模块除了数据不一样。其他都一样吧。

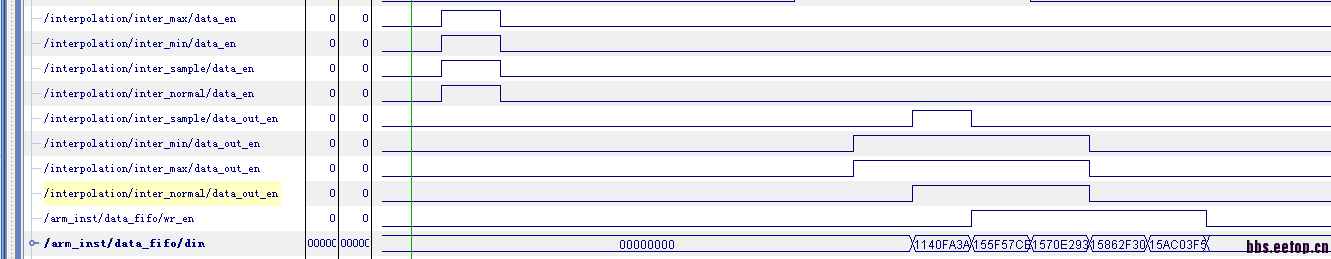

再贴chipscope

chipscope中4个模块的输入都一样。前面那四个en都对齐了。

问题就是输出不对。

max和min输出四个时钟拍的out_en,

但是sample输出的是两个个时钟拍的out_en,时序也没对齐。

同样normal只输出了三个时钟拍的out_en,时序延迟了一拍。

代表的是sample只输出了两个有效数据,normal只输出了三个有效数据。

那么在随后的FIFO中,长度为4个时钟拍的wr_en写进去的数值就错了。

还是要先清楚mix是做什么功能的,也许它就是要利用data_in内的一些信息来产生输出呢。