如何用ALTERA的PLL输出差分时钟?

时间:10-02

整理:3721RD

点击:

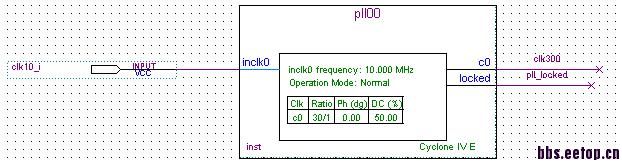

我想要FPGA输出一对300M的差分时钟,

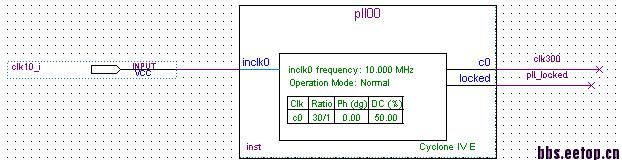

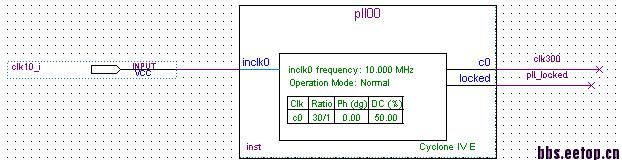

先用PLL倍频出一个300M时钟,

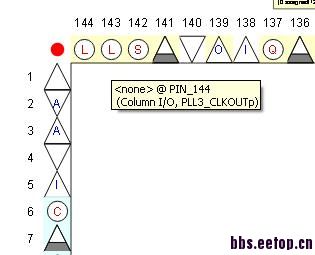

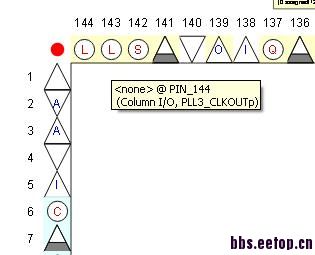

我不知道怎么把这个时钟和FPGA的PLL_CLKOUTp和PLL_CLKOUTn联系起来

图中的PIN_144和PIN_143是PLL_CLKOUTp和PLL_CLKOUTn。

怎么设置让这两个引脚输出PLL生成的300M时钟。

先用PLL倍频出一个300M时钟,

我不知道怎么把这个时钟和FPGA的PLL_CLKOUTp和PLL_CLKOUTn联系起来

图中的PIN_144和PIN_143是PLL_CLKOUTp和PLL_CLKOUTn。

怎么设置让这两个引脚输出PLL生成的300M时钟。

补图1:

有没有人知道怎么弄啊?

对于差分引脚,只需要指定信号到正极引脚。如果正极引脚被指定为差分I/O 标准,那么Quartus II 会自动指定负极引脚。

所以呢,你只需要将PLL的输出C0 分配到PLL_CLKOUTp,然后设置PLL_CLKOUTp 为差分IO,quartus II就会自动处理PLL_CLKOUTn,让PLL_CLKOUTp和PLL_CLKOUTn成为差分模式的IO

谢谢