altera pll的模拟问题

时间:10-02

整理:3721RD

点击:

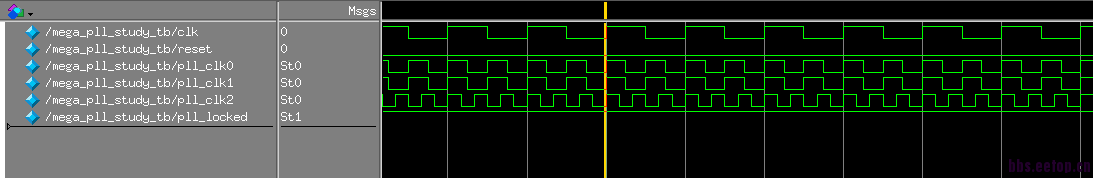

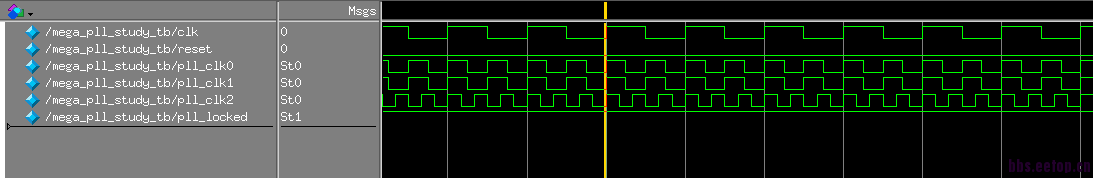

我在用modelsim模拟altera pll时遇到一个问题,按照altera的官方手册说明,如果pll的Operation Mode选择 Normal时,PLL输出的时钟波形(c0,c1,c2...)的上沿和输入时钟(inclk0)的上沿应该是对齐的。我建了一个最简单的pll实例,在modelsim模拟中,发现RTL模拟中输入输出时钟上沿对齐,但在Gatelevel模拟中,输出时钟明显滞后一段时间。请问这个现象是正常的吗?如果正常的话,在实际使用中,我是不是还要考虑由于输出时钟上沿都不对齐而导致要处理跨时域的问题,因为c0,c1,c2是分别驱动系统内不同模块的,模块间的数据传输就要受到这种时钟沿不一致的影响?1.RTL级模拟

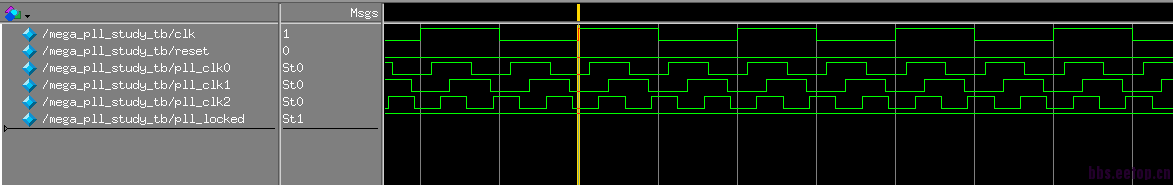

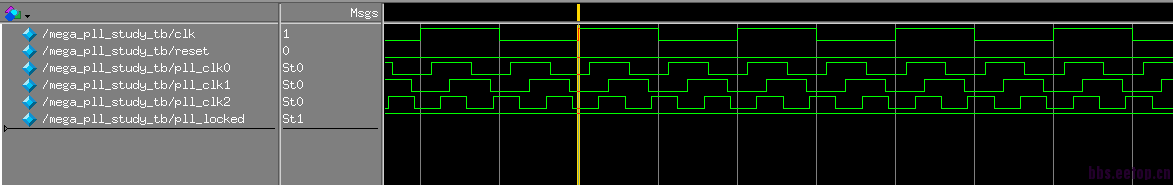

2.Gatelevel级模拟

2.Gatelevel级模拟

谢谢!

谢谢!

2.Gatelevel级模拟

2.Gatelevel级模拟 谢谢!

谢谢!