CPLD控制DAC,问题求教!

时间:10-02

整理:3721RD

点击:

用CPLD来控制DAC产生占空比一定的脉冲信号,testbench的仿真代码如下:

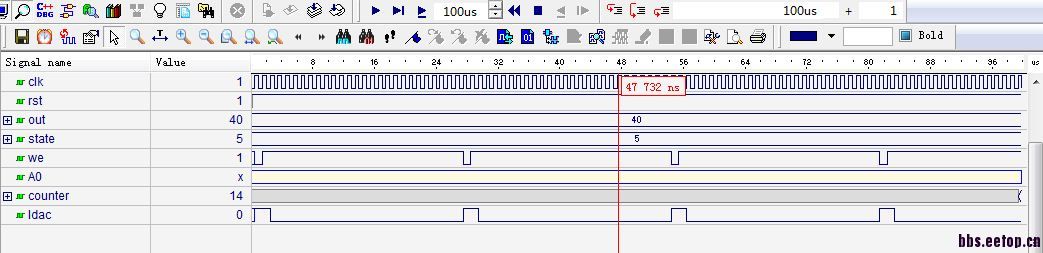

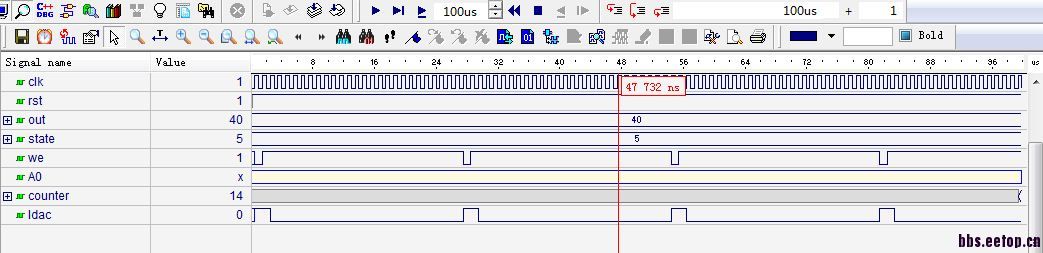

仿真结果如下:

不知为什么输出A0会出现问题?

同时,我用示波器测量ldac和we这两个输出引脚,结果都只是一个3.6V的直流量。

求指导

这样不仅可以避免combinational loop,也可以避免锁存器;但是在testbench中仿真出来的结果仍然和之前一样,AO输出口没有确切的输出。

- //-----------------------------------------------------------------------------

- //

- // Title : sim

- // Design : square1

- // Author :

- // Company :

- //

- //-----------------------------------------------------------------------------

- //

- // File : sim.v

- // Generated : Tue May 14 10:01:30 2013

- // From : interface description file

- // By : Itf2Vhdl ver. 1.22

- //

- //-----------------------------------------------------------------------------

- //

- // Description :

- //

- //-----------------------------------------------------------------------------

- `timescale 1 ns / 1 ns

- //{{ Section below this comment is automatically maintained

- // and may be overwritten

- //{module {sim}}

- module sim ();

- //}} End of automatically maintained section

- // -- Enter your statements here -- //

- reg clk,rst;

- wire [7:0] out;

- wire [3:0] state;

- wire we;

- wire A0;

- wire ldac;

- wire [4:0] counter;

- initial

- clk=0;

- always

- #500 clk=~clk;

-

- initial

- begin

- rst=1;

- #50 rst=0;

- #100 rst=1;

- end

- square tt(clk,rst,out,state,we,A0,ldac,counter);

-

- endmodule

- //利用TLV5613来画方波,通过控制写控制口的电平来调节方波的周期以及占空比;

- module square(clk,rst_n,out,state,we,A0,ldac,counter);

- input clk,rst_n;

- output wire [7:0] out;

- output [3:0] state; //从高位到低位,分别控制A1,SPD,片选以及PWD;

- output reg we; //控制TLV5613的写使能;

- output reg A0;//地址控制线A0

- output reg ldac;//输出控制线ldac

- reg rst;

- output reg [4:0] counter;//从0计数到26,不断循环

-

- assign state=5'b0101;

- assign out=8'b01000000;

-

- always @(posedge clk)

- rst=rst_n;

- always @(posedge clk or negedge rst)

- if(!rst)

- counter=0;

- else if(counter<26)

- counter=counter+1;

- else

- counter=0;

-

- always @(*)

- if(!rst)

- A0=0;

- else if(counter==0)

- A0=~A0;

-

- always @(*)

- if(!rst)

- we=1;

- else if(counter==0)

- we=0;

- else

- we=1;

-

- always @(*)

- if(!rst)

- ldac=1;

- else if(counter<2)

- ldac=1;

- else

- ldac=0;

-

-

-

- endmodule

仿真结果如下:

不知为什么输出A0会出现问题?

同时,我用示波器测量ldac和we这两个输出引脚,结果都只是一个3.6V的直流量。

求指导

always @(*)

if(!rst)

A0=0;

else if(counter==0)

A0=~A0;

Combinational loop

我对这段有问题的程序做了改正,如下:

- always @(posedge clk or negedge rst)

- if(!rst)

- A0=0;

- else if(counter==0)

- A0=A0+1;

- else A0=A0;

这样不仅可以避免combinational loop,也可以避免锁存器;但是在testbench中仿真出来的结果仍然和之前一样,AO输出口没有确切的输出。

fdsfdsfsfsfsfsdfsdfsdfsd

DAC是怎样的控制时序?

仿真波形中counter没有计数。