FPGA验证的问题

时间:10-02

整理:3721RD

点击:

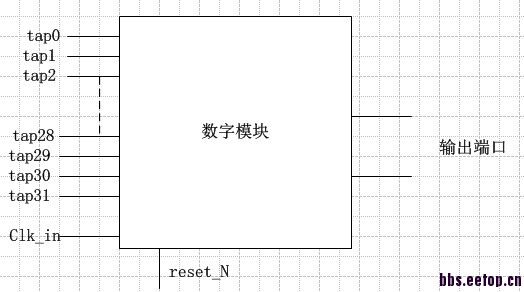

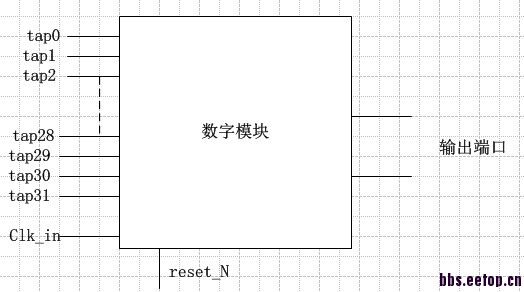

大家好,我现在手头上有个数字模块,但因为时钟端口太多,不知道这种数字模块能否用FPGA来验证,模块图如下

端口叙述:

tap0~tap31为时钟控制采样端口,频率同为100M,两个连续时钟的相位差为312.5ps,即就是他们为恒等相位差的32个时钟信号。

clk_in也是时钟信号,频率为10M。现在学校有一块红色飓风E45的开发板,老师叫我用它来验证这个数字电路的正确性,以前没玩过开发板。请问小弟该如何下手呢?望各位大神指点一下。多谢了

端口叙述:

tap0~tap31为时钟控制采样端口,频率同为100M,两个连续时钟的相位差为312.5ps,即就是他们为恒等相位差的32个时钟信号。

clk_in也是时钟信号,频率为10M。现在学校有一块红色飓风E45的开发板,老师叫我用它来验证这个数字电路的正确性,以前没玩过开发板。请问小弟该如何下手呢?望各位大神指点一下。多谢了

你好,如果tap0~tap31用时钟50M呢。因为它们是恒等相位差的时钟,如果用50M的话,相差为20n/32=625ps,这样的精度能达到吗?

clk_in还是用10M。这样可以吗?

很难,精度太高了,板子的走线延迟能满足这个精度?

这个估计够呛

内部能约束到保证和到FPGA 端口到信号时间间隔一致吗?

你好,我对开发板不太熟悉。如果要验证这个电路的话,这个32个恒等相位差的时钟信号该如何提供给它呢?开发板能有这么多时钟端口吗?

你好,如果要验证的话,这32个恒等相位差的时钟信号该如何提供给电路呢?开发板有这么多时钟端口吗?

端口数量可以满足,但是精度要求太高了

哦哦,请问如何从内部入手呢?它这32个时钟相位差如何设计提供呢?能否再讲详细点?求赐教了

哦,端口数量够了,但时钟数量呢?好像开发板不能提供这么多时钟吧?这32个相位差的时钟该如何进行设计提供给它测试呢?

哥们就是闲扯,说一下自己的思路。

可以在FPGA内部生成1个100m的clk,1个10mclk,100m的clk通过一个特殊的组合逻辑或者布线产生32组延迟为312.5ps的时钟接入数字模块,不知是否可行

特殊的组合逻辑,看过一个资料,可以用加法器的进位端,据文章讲可以达到70~80ps的精度

小编再研究下

应该可以实现吧

多谢指点了,很有用的思路,我再研究研究。

VERY GOOD