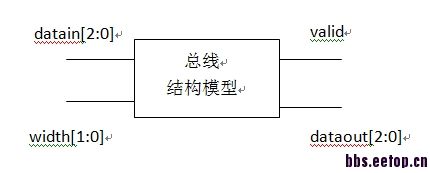

关于总线传输数据的一些问题,求教

传输机制是怎么样的?

我认为是里面有寄存器存储数据,存够8位再输出,他说不够详细。求高手说说完整的传输过程,谢谢了。

用个fifo就可以

几乘几的FIFO啊,宽度是8位深度随便吗?

存够8位再输出的话该模块肯定是要有存储元件了。

输出数据由valid显示那为handshaking提供了可能。

话说这个模块连clk都没有大丈夫?

他只是大概说了下,可以加上CLK什么的,主要是怎么实现他说的功能。e

蛮力。

功能:当输入数据满8位时,dataout(7:0)输出最近输入的8位数据并置valid为1,valid=1持续一个时钟周期。dataout高位是最新的数据,dataout低位是最老的数据。

输入的数据会先保存在寄存器中,FSM的每一个状态表示已经保存的数据的位数。当最新输入的数据位数加已经保存的数据位数等于8时,输出这8位数据并置valid为1。这里也要考虑到当输入的位数可能不与8位对齐,比如输入端的数据位数可能第一个时钟周期3位,第二个时钟周期3位,第三个时钟周期1位,第四个时钟周期3位,这时第四个时钟周期输入的其中2位数据就要被归在下一组8位输出

伪代码:

- initilization:

- data(7:0)="00000000"

- overflow_width(1:0)="00"

- overflow_data(1:0)="00"

- state = 0

- @rising edge of clk

- FSM:

- state 0

- valid = "0"

- if width="01"

- data(0) = datain(0)

- state = 1

- else if width="10"

- data(1:0) = datain(1:0)

- state = 2

- else if width="11"

- data(2:0) = datain(2:0)

- state = 3

- else

- state = 0

- endif

- state 1

- valid = "0"

- if width="01"

- data(1) = datain(0)

- state = 2

- else if width="10"

- data(2:1) = datain(1:0)

- state = 3

- else if width="11"

- data(3:1) = datain(2:0)

- state = 4

- else

- state = 1

- endif

- .

- .

- .

- state N

- #if N=2# valid = "0" #endif#

- if width="01"

- data(N) = datain(0)

- state = N+1

- else if width="10"

- data(N+1:N) = datain(1:0)

- state = N+2

- else if width="11"

- data(N+2:N) = datain(2:0)

- state = N+3

- else

- state = N

- endif

- .

- .

- .

- state 6:

- if width="01"

- data(6) = datain(0)

- state = 7

- else if width="10"

- dataout(7:6) = datain(1:0)

- dataout(5:0) = data(5:0)

- valid = "1"

- state = 0

- else if width="11"

- dataout(7:6) = datain(1:0)

- dataout(5:0) = data(5:0)

- valid = "1"

- data(0) = datain(2)

- state = 1

- else

- state = 6

- endif

-

- state 7:

- if width="01"

- dataout(7) = datain(0)

- dataout(6:0) = data(6:0)

- valid = "1"

- state = 0

- else if width="10"

- dataout(7) = datain(0)

- dataout(6:0) = data(6:0)

- data(0) = datain(1)

- valid = "1"

- state = 1

- else if width="11"

- dataout(7) = datain(0)

- dataout(6:0) = data(6:0)

- data(1:0) = datain(2:1)

- valid = "1"

- state = 2

- else

- state = 7

- endif

这是拿什么写的啊,有点看不明白,我今天跟同学讨论了下,用16位宽的FIFO应该可以的。

呃。不知道你是用verilog还是vhdl,所以就用的伪代码来表达一下实现思想

我很好奇怎样用FIFO来实现。16位是如位定的呢。valid又怎么给呢

感觉FIFO就可以实现,或者弄个计数器就行啦。

用FIFO写数据,当指针大于8了就输出前8位数据,并置valid为1,因为输入数据位数不确定,所以设定位宽大点,保证能满足功能

举个例子:

在四个时钟周期里的输入分别是

datain = 001, width = 01 有效数据是1

datain = 001, width = 01 有效数据是1

datain = 001, width = 10 有效数据是01

datain = 001, width = 11 有效数据是001

假设最先输入数据是先低位后高位,那最终输出的8位数据就应该是0010111

如果用FIFO的话,是不是就是把datain存进去?那如果按上面的例子,指针为4的时候就应该valid=1了,并且又如何从FIFO中选出那有效8位数据呢

width是当前输入数据的位数,按你这个例子应该是:datain = 001, width = 11

datain = 001, width = 11

datain = 001, width = 11

datain = 001, width = 11

这已经进来12位数据了,指针已经大于8了,其实当指针大于8的时候,说明已经存够8位数据了,这时候就置valid为1,输出数据了

嗯,看来是我把问题想复杂了,原来对每一次8位数据传输,width是固定不变的。