在实际设计中时序约束参数如何设置?

input delay是已知条件,取决于片外输入信号的特性。output delay是对综合结果的要求,就是你希望输出数据比时钟延时多少。

5555,现在对这个都没概念……都不知道已知参数及自己想要的参数是几多……

可以baidu两篇相关文档先看看,看能否帮助认知

1“TimeQuest就一定要搞定”

2“瞎搞TimeQuest的无责任笔记”

谢谢回答~TimeQuest就一定要搞定看过,另外一个没看过……还是觉得TimeQuest User Guide (By: Ryan Scoville)写的稍好一点儿……也看过几本关于时序约束的英文书,了解相关时序分析及约束的几本理论……But I have difficulties in deciding the values to be used.

http://www.altera.com/customertraining/webex/SourceSynchTiming/player.html

看一下这个你就差不多了解了,Altera官方教程。

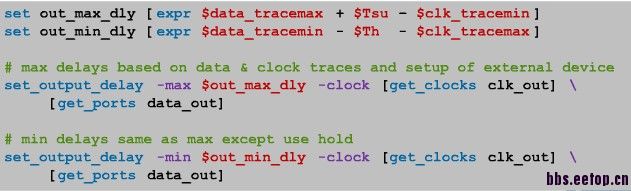

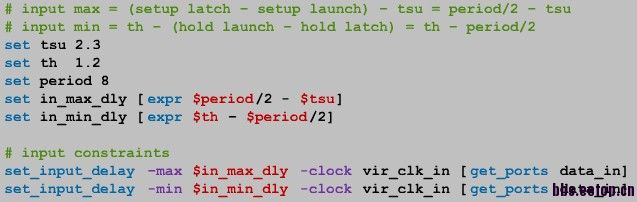

谢谢小编帮助!我貌似看过一个官方教学视频……我就是不懂这些参数从哪里来……比如:

这些红色的参数都是怎么设定的?

还有个疑惑的地方:如何确定要分析的模块?

才发现原来是小编~~谢谢小编的热心帮助!小女子是个菜鸟,只能来论坛上乱问了……

恩,一针见血,是缺乏实践……因为研究生期间,都是一个人摸索这个,比较困难……哎……

我也搞不懂这个

这些参数都是根据PCB走线长度、驱动器件时序特性、设计内部时钟频率而来的。比如DDR器件要求一定的建立时间Tsu和保持时间th等,走线长度决定输入延时,输出延时,时钟延时。当然这些参数也根据FPGA内部布线结果不同产生变化。你需要做的就是告诉STA工具外部它不知道的参数。然后STA工具会根据这些参数结合自己的布线结果进行分析。

明白一点了……就是我必须知道设计应该需要什么样的时序,然后就往哪方面约束?谢谢小编帮助!