请教一个primetime静态时序仿真的问题

我总是感觉PT做静态时序仿真必须得有clk在才好,只有这样,报告中才能比较arrival time和时钟周期,得到slack(正数是满足,负数不满足)。这就是我对PT的弱弱的理解。

于是我让设计这个电路的人只在输出端 加了reg(输入端不可以加reg?),于是就有了clk了:

module hisdesign(clk, A,B, C);

input [32:1] A;

input [32:1] B;

input clk;

output [32:1] C;

reg [32:1] C;

wire [32:1] output_c;

multiplier mul(A,B, output_c); //代表”门级组合电路。“

always @(posedge clk)

C<=output_c;

endmodule

我先拿DC综合出某个库的门级verilog,然后用PT做时序分析,

静态时序仿真的结果和我想象的不一样,我开始慢慢感觉到错在哪里了,但是不知道怎么改:

Startpoint: C_reg[1]

(rising edge-triggered flip-flop clocked by clk)

Endpoint: C[1] (output port clocked by clk)

Path Group: clk

Path Type: max

Point Incr Path

---------------------------------------------------------------

clock clk (rise edge) 0.00 0.00

clock network delay (ideal) 0.00 0.00

C_reg[1]/CK (DFFRQX2VH) 0.00 0.00 r

C_reg[1]/Q (DFFRQX2VH) 7.90 7.90 r

C[1] (out) 0.00 7.90 r

data arrival time 7.90

clock clk (rise edge) 10.00 10.00

clock network delay (ideal) 0.00 10.00

output external delay -1.00 9.00

data required time 9.00

---------------------------------------------------------------

data required time 9.00

data arrival time -7.90

---------------------------------------------------------------

slack (MET) 1.10

以上就是我的仿真结果,感觉不是我原本想算的东西,请高手们帮忙看下啊,谢谢。

是怎么设置的约束?

C_reg[1]/CK (DFFRQX2VH) 0.00 0.00 r

C_reg[1]/Q (DFFRQX2VH) 7.90 7.90 r

C[1] (out) 0.00 7.90 r

感觉乘法器的逻辑是空的(没有读进去)? 路径里面只包含了寄存器的cell delay

可以在输入端都加上Register,这样就输入、输出都是基于clk。你再试一试。

纯组合电路也可以分析时序,不然怎么综合优化呢。

你的SDC和时序报告的命令都贴出来吧。

时序分析一般是寄存器之间, 你只有输出有reg , 输入没有reg, 那你这个怎么分析?到时候你和外部顶层的连接起来有可能在顶层上时序过不去

报一下 输入a-》寄存器c 以及 B-》c 的timing

多谢各位大侠指点。

我之前给的代码好像不全。

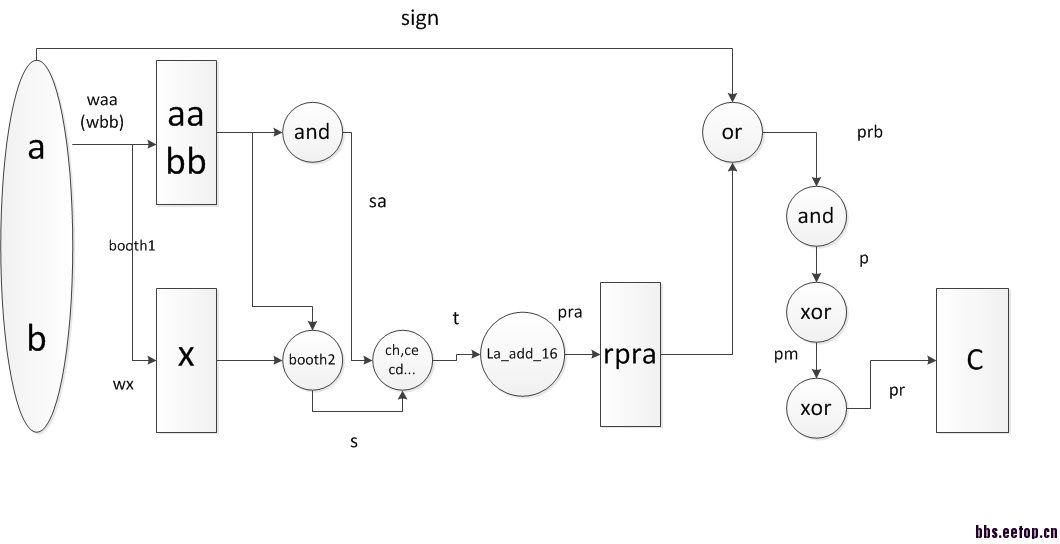

原电路就是一个组合逻辑,没有一个寄存器。但是那个设计者为了故意把电路拆成4个周期,在中间加了一些寄存器,他强调说他想试着实现4级流水线电路。但是我从他的代码中提取出的结构如下图所示:

矩形代表寄存器,圆形或者椭圆都是组合逻辑。

我感觉他直接把sign这个信号输入给最后一级的组合电路不太对吧?(应该sign=>sign1=>sign2也分级来传吧?)

而且不太像是4级流水线。

请问本贴中遇到的时序仿真问题是不是和这个有关?

没有看懂呢!

你应该设input delay,外部用虚拟clock,

你现在是组合逻辑的输出连到一个reg的输入,你的constrain设的不对

多谢大侠。

我有个疑问,假如就是有一条没有输入寄存器的路径,只有输出寄存器C,

是不是PT得到的结果一定是这条路径 max_delay? 因为找不到输入关卡,所以认为delay无限大?

然而,输出的delay数字却是C_reg的CLK->Q延时?

我知道我这个电路分析一定是我错了,但是不知道分析的对不对。

针对只有寄存器输出的路径,我个人认为大多数都是静态配置信号,如果是数据路径的话,一般都会用寄存器寄存的,静态信号一般都是一个稳定的值,所以对最后输出的寄存器来说时序是没什么问题的。就按照你的假设,整条路径的最大delay就是该信号从模块输入到寄存器前所有逻辑门的延时,不是无穷大的。在模块设计中最好不要有这样的路径出现。

呵呵,比较有意思的问题

看了 半天 还是没有解决问题吗?