DC导出的网表疑问

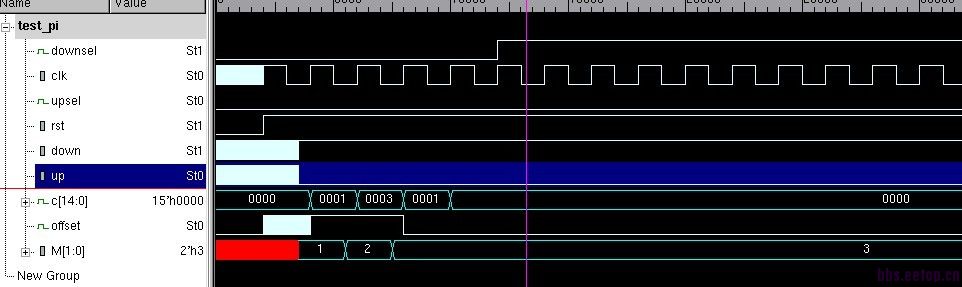

前仿真波形

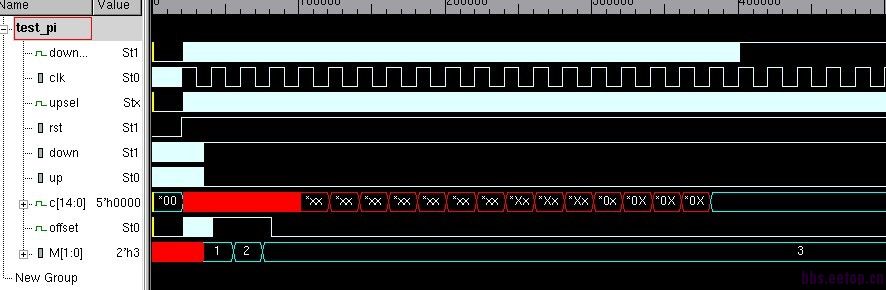

DC的网表仿真波形

其中:input clk,rst;

input up,down;

input [1:0]M;

output upsel,downsel;

output offset;

output [14:0]c;

这个要根据信号关系来查看引入X的原因;

最好给收入信号给初值。

应该是输入信号刚打错了

推测是vcs的library和DC的library不一致 或者时序不一致 你有试过在vcs里annotate SDF吗?

你好,我用其他设计试过,已经确定vcs的library和DC的library是一致的,也就是说其他设计DC后的网表的仿真都跟前仿是一样的。就说明应该不是库的问题。我也试过用annotate SDF,DC的综合过程没有任何时序违例。 但针对现在出问题的这个设计,也是同样的出现上图的不定状态。请再指点下,谢谢了。我会把源程序跟测试程序都贴出来,麻烦你再帮我看看。

你好,我用其他设计试过,已经确定vcs的library和DC的library是一致的,也就是说其他设计DC后的网表的仿真都跟前仿是一样的。就说明应该不是库的问题。我也试过用annotate SDF,DC的综合过程没有任何时序违例。 但针对现在出问题的这个设计,也是同样的出现上图的不定状态。请再指点下,谢谢了。我会把源程序跟测试程序都贴出来,麻烦你再帮我看看

你好,我把源程序跟测试代码都贴出来吧。请麻烦你帮我看看。我 DC综合过程没有报任何时序违例, 也能确定库用的是正确的,其他设计这是这样跑流程的,都没出现过这种问题。但目前的设计就碰到这种问题,还请再指教小弟一下。两个子程序如下:

`timescale 1ns/10ps

module mux(clk,rst,upsel,downsel,M);

input clk,rst;

input upsel,downsel;

output [1:0]M;

reg [1:0]M;

parameter first=2'b00,

second=2'b10,

third=2'b11,

fourth=2'b01;

always @(posedge clk or negedge rst)

if(!rst)

M<=first;

else

case(M)

first: if(upsel==1'b1)

M<=fourth;

else if(downsel==1'b1)

M<=second;

else

M<=first;

second: if(upsel==1'b1)

M<=first;

else if(downsel==1'b1)

M<=third;

else

M<=second;

third: if(upsel==1'b1)

M<=second;

else if(downsel==1'b1)

M<=fourth;

else

M<=third;

fourth: if(upsel==1'b1)

M<=third;

else if(downsel==1'b1)

M<=first;

else

M<=fourth;

default: M<=2'bx;

endcase

endmodule

`timescale 1ns/10ps

module pi(clk,rst,up,down,M,upsel,downsel,offset,c);

input clk,rst;

input up,down;

input [1:0]M;

output upsel,downsel;

output offset;

output [14:0]c;

reg [14:0] c;

reg upsel,downsel,offset;

wire[1:0]M;

wire up,down;

wire clk,rst;

parameter c_0=15'b000_0000_0000_0000,

c_1=15'b000_0000_0000_0001,

c_2=15'b000_0000_0000_0011,

c_3=15'b000_0000_0000_0111,

c_4=15'b000_0000_0000_1111,

c_5=15'b000_0000_0001_1111,

c_6=15'b000_0000_0011_1111,

c_7=15'b000_0000_0111_1111,

c_8=15'b000_0000_1111_1111,

c_9=15'b000_0001_1111_1111,

c_10=15'b000_0011_1111_1111,

c_11=15'b000_0111_1111_1111,

c_12=15'b000_1111_1111_1111,

c_13=15'b001_1111_1111_1111,

c_14=15'b011_1111_1111_1111,

c_15=15'b111_1111_1111_1111;

always @(posedge clk or negedge rst)

if(!rst)

begin

c<=c_0;

upsel<=0;

downsel<=0;

end

else

case(c)

c_0:

begin

if(((M==2'b00||M==2'b11)&&(up==1&&down==0))||((M==2'b10||M==2'b01)&&(up==0&&down==1)))

c<=c_1;

else if((M==2'b00||M==2'b11)&&(up==0&&down==1))begin

downsel<=1;c<=c_0;end

else if((M==2'b10||M==2'b01)&&(up==1&&down==0))begin

upsel<=1;c<=c_0;end

else

c<=c_0;

end

c_1: if(((M==2'b00||M==2'b11)&&(up==1&&down==0))||((M==2'b10||M==2'b01)&&(up==0&&down==1)))

c<=c_2;

else if(((M==2'b00||M==2'b11)&&(up==0&&down==1))||((M==2'b10||M==2'b01)&&(up==1&&down==0)))

c<=c_0;

else

c<=c_1;

c_2: if(((M==2'b00||M==2'b11)&&(up==1&&down==0))||((M==2'b10||M==2'b01)&&(up==0&&down==1)))

c<=c_3;

else if(((M==2'b00||M==2'b11)&&(up==0&&down==1))||((M==2'b10||M==2'b01)&&(up==1&&down==0)))

c<=c_1;

else

c<=c_2;

c_3: if(((M==2'b00||M==2'b11)&&(up==1&&down==0))||((M==2'b10||M==2'b01)&&(up==0&&down==1)))

c<=c_4;

else if(((M==2'b00||M==2'b11)&&(up==0&&down==1))||((M==2'b10||M==2'b01)&&(up==1&&down==0)))

c<=c_2;

else

c<=c_3;

c_4: if(((M==2'b00||M==2'b11)&&(up==1&&down==0))||((M==2'b10||M==2'b01)&&(up==0&&down==1)))

c<=c_5;

else if(((M==2'b00||M==2'b11)&&(up==0&&down==1))||((M==2'b10||M==2'b01)&&(up==1&&down==0)))

c<=c_3;

else

c<=c_4;

c_5: if(((M==2'b00||M==2'b11)&&(up==1&&down==0))||((M==2'b10||M==2'b01)&&(up==0&&down==1)))

c<=c_6;

else if(((M==2'b00||M==2'b11)&&(up==0&&down==1))||((M==2'b10||M==2'b01)&&(up==1&&down==0)))

c<=c_4;

else

c<=c_5;

c_6: if(((M==2'b00||M==2'b11)&&(up==1&&down==0))||((M==2'b10||M==2'b01)&&(up==0&&down==1)))

c<=c_7;

else if(((M==2'b00||M==2'b11)&&(up==0&&down==1))||((M==2'b10||M==2'b01)&&(up==1&&down==0)))

c<=c_5;

else

c<=c_6;

c_7: if(((M==2'b00||M==2'b11)&&(up==1&&down==0))||((M==2'b10||M==2'b01)&&(up==0&&down==1)))

c<=c_8;

else if(((M==2'b00||M==2'b11)&&(up==0&&down==1))||((M==2'b10||M==2'b01)&&(up==1&&down==0)))

c<=c_6;

else

c<=c_7;

c_8: if(((M==2'b00||M==2'b11)&&(up==1&&down==0))||((M==2'b10||M==2'b01)&&(up==0&&down==1)))

c<=c_9;

else if(((M==2'b00||M==2'b11)&&(up==0&&down==1))||((M==2'b10||M==2'b01)&&(up==1&&down==0)))

c<=c_7;

else

c<=c_8;

c_9: if(((M==2'b00||M==2'b11)&&(up==1&&down==0))||((M==2'b10||M==2'b01)&&(up==0&&down==1)))

c<=c_10;

else if(((M==2'b00||M==2'b11)&&(up==0&&down==1))||((M==2'b10||M==2'b01)&&(up==1&&down==0)))

c<=c_8;

else

c<=c_9;

c_10: if(((M==2'b00||M==2'b11)&&(up==1&&down==0))||((M==2'b10||M==2'b01)&&(up==0&&down==1)))

c<=c_11;

else if(((M==2'b00||M==2'b11)&&(up==0&&down==1))||((M==2'b10||M==2'b01)&&(up==1&&down==0)))

c<=c_9;

else

c<=c_10;

c_11: if(((M==2'b00||M==2'b11)&&(up==1&&down==0))||((M==2'b10||M==2'b01)&&(up==0&&down==1)))

c<=c_12;

else if(((M==2'b00||M==2'b11)&&(up==0&&down==1))||((M==2'b10||M==2'b01)&&(up==1&&down==0)))

c<=c_10;

else

c<=c_11;

c_12: if(((M==2'b00||M==2'b11)&&(up==1&&down==0))||((M==2'b10||M==2'b01)&&(up==0&&down==1)))

c<=c_13;

else if(((M==2'b00||M==2'b11)&&(up==0&&down==1))||((M==2'b10||M==2'b01)&&(up==1&&down==0)))

c<=c_11;

else

c<=c_12;

c_13: if(((M==2'b00||M==2'b11)&&(up==1&&down==0))||((M==2'b10||M==2'b01)&&(up==0&&down==1)))

c<=c_14;

else if(((M==2'b00||M==2'b11)&&(up==0&&down==1))||((M==2'b10||M==2'b01)&&(up==1&&down==0)))

c<=c_12;

else

c<=c_13;

c_14: begin

if(((M==2'b00||M==2'b11)&&(up==1&&down==0))||((M==2'b10||M==2'b01)&&(up==0&&down==1)))

c<=c_15;

else if(((M==2'b00||M==2'b11)&&(up==0&&down==1))||((M==2'b10||M==2'b01)&&(up==1&&down==0)))

c<=c_13;

else

c<=c_14;

end

c_15: begin upsel<=0;downsel<=0;

if(((M==2'b00||M==2'b11)&&(up==0&&down==1))||((M==2'b10||M==2'b01)&&(up==1&&down==0)))

c<=c_14;

else if((M==2'b00||M==2'b11)&&(up==1&&down==0))begin

upsel<=1;c<=c_15;end

else if((M==2'b10||M==2'b01)&&(up==0&&down==1))begin

downsel<=1;c<=c_15;end

else c<=c_15;

end

default:c<=15'x;

endcase

always @(posedge clk or negedge rst)

begin

if(!rst)

offset<=0;

else

offset<=M[1]^M[0];

end

endmodule

顶层模块:

`timescale 1ns/10ps

module pimux(clk,rst,up,down,c,M,offset);

input clk,rst;

input up,down;

output[1:0]M;

output[14:0]c;

wire up,down;

wire clk,rst;

wire upsel,downsel;

output offset;

mux u1(.clk(clk),.rst(rst),.upsel(upsel),.downsel(downsel),.M(M));

pi s1(.clk(clk),.rst(rst),.up(up),.down(down),.M(M),.upsel(upsel),.downsel(downsel),.offset(offset),.c(c));

endmodule

测试文件如下:

`timescale 1ns/10ps

module test_pimux;

initial

begin

$sdf_annotate ("pimux.sdf",pimux);

end

reg up,down;

reg clk,rst;

wire[1:0]M;

wire offset;

wire[14:0]c;

pimux pimux(clk,rst,up,down,c,M,offset);

always #10 clk=~clk;

initial

begin

rst=0;

#10 rst=1;

clk=0;

up=1;

down=0;

#400 up=0;

down=1;

#1000;

end

endmodule

以上就是详细信息,就是简单的两个状态机相连,前仿的波形都很好,但DC的网表不管加不加延时文件都是出来的是x,请大家指点一下,谢谢!~

#10 rst = 1;

clk = 0

改为

clk = 0

#15 rst = 1;

应该就可以了。

我试过了,果然可以了。太感谢了你, 原来不是网表的问题,是我的测试文件没写好。小弟受教了!

解决了好,我刚上网,没来得及看

你好,还有个小问题想请教一下。DC导出来的网表是不是可以直接拿来仿真呢?但是我的设计,如果只加DC导出的网表仿真,结果还是全X状态,但如果网表再加入DC导出的sdf文件的话,波形就是正确的。

所以,我想请教一下,①既然DC导出的sdf文件不准确,是不是可以直接仿真网表不加延时文件就能确定功能的正确性嘛?

②像我现在这个设计,DC的网表单独仿真还是出现X状态,但在网表的基础上加入延时文件,波形就正确的。这还能说明我的设计是正确的吗?

不加SDF的话,有时GATE会使用库里的默认延迟,而用这个延迟量可能会有问题。

你可以在VCS compile时加-notimingcheck,再看仿真结果。