第一次使用ALTERA的ALTLVDS,诸多问题,还请大家不吝赐教

时间:10-02

整理:3721RD

点击:

大家好,我是新手,以前都是用verilog设计输入,现在第一次用到IP核,用的是QUARTUS II 的ALTLVDS,出现了很多问题,只好请教下大家了。

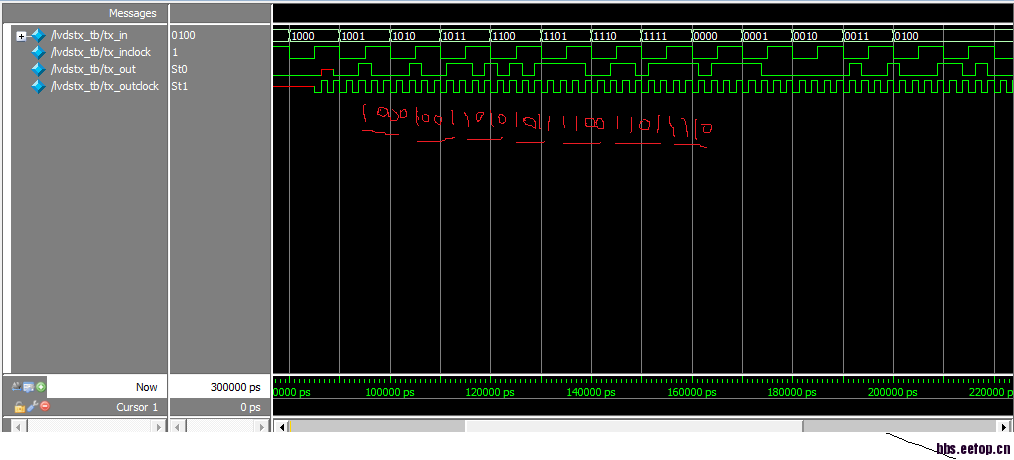

因为以前没用过,所以只是简单的调用了下ALTLVDS模块,然后想编个testbench看看时序。但是最后时序出来的时候我却有点不明白,结果是对的

1. 但是在tx_in从0000-0111的时候,输出时钟tx_outclock输出一直为X态,而且tx_outclock有效后,tx_in=1000的输出也比输入滞后了一个周期多,这个是为什么?

2. 我还想问下,tx_in的输入是在tx_inclock的上升沿还是下降沿进入到lvds接口的。因为这个altera的手册里没有说,altera的手册里连个时序图都没有,郁闷。

3. 我用的是Arria II GX器件,我分配引脚的时候输出引脚tx_outclock和tx_out 总是出错,错误如下:Error: Can't place differential I/O transmitter pin tx_outclock in location AK15 -- differential I/O pin requires dedicated I/O SERDES, but location does not have differential I/O transmitter SERDES available。 这个看字面意思是需要SERDES,但我只是用了下lvds接口呀,没有用到SERDES接口,请问怎么解决这个错误。

因为是新手,问题有点多,希望大侠们能够帮忙解答下,多谢了。

小心翼翼顶下,别沉了,等高手

1. 你指仿真开始的时候出现X态吧?最开始一段时间仿真有这状态是正常的,你仿真其它IP CORE有时也出现类似的情况,得等一定周期后才出现有效的输出。 晚一个周期多,因为不是组合逻辑直接输出,会有延迟。

2. 一般来讲默认都是时钟上升沿,DDR数据是上下尚都会打数。

3. 就是这个PIN脚不支持PN数据,你换个其它位置看看。你这是简单地将并行数据转为差分串行数据输出,在底层实现时也使用了SERDES吧。

我用Q II 9.0 版本编译就可以通过 ,用 10.0换了好几个引脚都不行,不知道为什么。

我是新手,不太理解“在底层实现时也使用了SERDES吧” 这个是什么意思,SERDES不是有专用引脚吗?

要么你试着用10.0的CORE生成器再生成一遍ALTLVDS,然后再试,我也发生过9.1的工程放在10.0上跑不过,并且以前生成的CORE用新的merge生成器打不开的情况,最后为了与他人保持一致,又装了9.1的