关于组合反馈的问题

时间:10-02

整理:3721RD

点击:

设计综合,工具报告出现了组合反馈。根据工具提示,应该是这部分代码出了问题,如下:always @ ( posedge hclk_gt or negedge hrstn ) begin

if ( !hrstn )

refer_ok_hclk <= 'b0;

else begin

if ( !break ) begin

if ( beg_region && count_1023_hclk )

refer_ok_hclk <= 1'b1;

else

refer_ok_hclk <= 'b0;

end

else

refer_ok_hclk <= 'b0;

end

end

请问是否是这部分出了组合反馈?怎样判断会出现组合反馈?怎样避免呢?无意识的组合反馈的危害有哪些?请高手解答啊!

这是代码:

always @ ( posedge hclk or negedge hrstn )

if ( !hrstn )

EN_int_req_reg <= 'b0;

else

EN_int_req_reg <= EN_int_req;

// "EN_gen_req"

always @ ( posedge hclk or negedge hrstn )

if ( !hrstn )

EN_gen_req <= 'b0;

else if ( int_req_eva || int_req_xy || int_req_sum )

EN_gen_req <= 1'b1;

else

if ( EN_int_req && !EN_int_req_reg )

EN_gen_req <= 'b0;

else

EN_gen_req <= EN_gen_req;

// "clear" will be active if "1 == row_y_pic" and "count_1023_hclk"

// is active.

always @ ( posedge hclk or negedge hrstn )

if ( !hrstn )

clear <= 'b0;

else if ( int_req_cfg )

clear <= 'b0;

else

if ( 1 == row_y_pic && count_1023_hclk )

clear <= 1'b1;

else

clear <= clear;

/** ^ Generate "refer_ok" which is in-phase with "ad_clk" ^ **/

// "hclk_gt" will be assign to "hclk" while "stall_b" is active.

assign hclk_gt = stall_b && hclk;

// Generate "stall_b"

always @ ( refer_ok_hclk or ref_ok_s2f2 )

if ( ref_ok_s2f2 )

stall_b = 1'b1;

else

if ( refer_ok_hclk )

stall_b = 'b0;

else

stall_b = 1'b1;

// Generate "ref_ok_s2f1"

always @ ( posedge hclk or negedge hrstn )

if ( !hrstn )

ref_ok_s2f1 <= 'b0;

else

if ( refer_ok )

ref_ok_s2f1 <= 1'b1;

else

ref_ok_s2f1 <= 'b0;

// Generate "ref_ok_s2f2"

always @ ( posedge hclk or negedge hrstn )

if ( !hrstn )

ref_ok_s2f2 <= 'b0;

else

ref_ok_s2f2 <= ref_ok_s2f1;

// The "beg_region" will be set to "1" while "row_y_pic"

// reach the first row of the last 3 "1/4 region".

assign beg_region = ( 256 == row_y_pic || 512 == row_y_pic )

? 1'b1

: ( 768 == row_y_pic || 0 == row_y_pic)

? 1'b1

: 'b0;

// "refer_ok_hclk" will be set to "1" if "beg_region" while

// "count_1023_hclk" is active and "break" is inactive.

always @ ( posedge hclk_gt or negedge hrstn ) begin

if ( !hrstn )

refer_ok_hclk <= 'b0;

else begin

if ( !break ) begin

if ( beg_region && count_1023_hclk )

refer_ok_hclk <= 1'b1;

else

refer_ok_hclk <= 'b0;

end

else

refer_ok_hclk <= 'b0;

end

end

// Generate "ref_ok_f2s1"

always @ ( posedge ad_clk or negedge hrstn )

if ( !hrstn )

ref_ok_f2s1 <= 'b0;

else

if ( refer_ok_hclk )

ref_ok_f2s1 <= 1'b1;

else

ref_ok_f2s1 <= 'b0;

// Generate "ref_ok_f2s2" and "ref_ok_f2s3".

always @ ( posedge ad_clk or negedge hrstn )

if ( !hrstn )

{ ref_ok_f2s3, ref_ok_f2s2 } <= 2'b00;

else

{ ref_ok_f2s3, ref_ok_f2s2 } <= { ref_ok_f2s2, ref_ok_f2s1 };

// Generate "refer_ok"

always @ ( ref_ok_f2s3 or ref_ok_f2s2 )

case ( { ref_ok_f2s3, ref_ok_f2s2 } )

2'b01 : refer_ok = 1'b1;

default : refer_ok = 'b0;

endcase

/** v Generate "refer_ok" which is in-phase with "ad_clk" v **/

//---------------------------------------------------------------------

/********** ^ Generate "int_req" ^ **********/

// Generate "count_1023_hclk".

assign count_1023_hclk = ( count_1023_pic && !count_1023_pic_reg )

? 1'b1

: 'b0;

// "count_1023_pic_reg" is a circle later than "count_1023_pic"

always @ ( posedge hclk or negedge hrstn )

if( !hrstn )

count_1023_pic_reg <= 'b0;

else

count_1023_pic_reg <= count_1023_pic;

// "beg_region_reg"

always @ ( posedge hclk or negedge hrstn )

if ( !hrstn )

beg_region_reg <= 'b0;

else

beg_region_reg <= beg_region;

// Indicate the generation of "int_req" to CPU to read the row

// of "0", "256", "512" and "768".

always @ ( posedge hclk or negedge hrstn )

if ( !hrstn )

beg_region_index <= 'b0;

else if ( int_req_ref_ok )

beg_region_index <= 'b0;

else

if ( beg_region && !beg_region_reg )

beg_region_index <= 1'b1;

else

beg_region_index <= beg_region_index;

if ( !hrstn )

refer_ok_hclk <= 'b0;

else begin

if ( !break ) begin

if ( beg_region && count_1023_hclk )

refer_ok_hclk <= 1'b1;

else

refer_ok_hclk <= 'b0;

end

else

refer_ok_hclk <= 'b0;

end

end

请问是否是这部分出了组合反馈?怎样判断会出现组合反馈?怎样避免呢?无意识的组合反馈的危害有哪些?请高手解答啊!

组合反馈跟这块应该没关系

多看看你的组合逻辑生成部分代码

这段代码应该不会生成组合反馈的,把报告贴出来看看,还有把代码全贴出来,问题应该不在这儿

下面的语句会出现组合反馈,不写类似的语句就没有问题

1. assign b = sel ? a : b;

2.非时钟触发的always块中不写else

always@(*)

begin

if(sel)

b <= a;

end

3.

always@(*)

begin

if(sel)

b <= a;

else

b<=b;

end

你这段是时序逻辑吧,怎么会有组合反馈

只有这段代码看不出什么啊

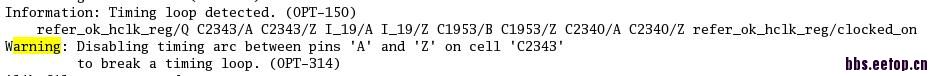

这是综合出来的报告:

这是代码:

always @ ( posedge hclk or negedge hrstn )

if ( !hrstn )

EN_int_req_reg <= 'b0;

else

EN_int_req_reg <= EN_int_req;

// "EN_gen_req"

always @ ( posedge hclk or negedge hrstn )

if ( !hrstn )

EN_gen_req <= 'b0;

else if ( int_req_eva || int_req_xy || int_req_sum )

EN_gen_req <= 1'b1;

else

if ( EN_int_req && !EN_int_req_reg )

EN_gen_req <= 'b0;

else

EN_gen_req <= EN_gen_req;

// "clear" will be active if "1 == row_y_pic" and "count_1023_hclk"

// is active.

always @ ( posedge hclk or negedge hrstn )

if ( !hrstn )

clear <= 'b0;

else if ( int_req_cfg )

clear <= 'b0;

else

if ( 1 == row_y_pic && count_1023_hclk )

clear <= 1'b1;

else

clear <= clear;

/** ^ Generate "refer_ok" which is in-phase with "ad_clk" ^ **/

// "hclk_gt" will be assign to "hclk" while "stall_b" is active.

assign hclk_gt = stall_b && hclk;

// Generate "stall_b"

always @ ( refer_ok_hclk or ref_ok_s2f2 )

if ( ref_ok_s2f2 )

stall_b = 1'b1;

else

if ( refer_ok_hclk )

stall_b = 'b0;

else

stall_b = 1'b1;

// Generate "ref_ok_s2f1"

always @ ( posedge hclk or negedge hrstn )

if ( !hrstn )

ref_ok_s2f1 <= 'b0;

else

if ( refer_ok )

ref_ok_s2f1 <= 1'b1;

else

ref_ok_s2f1 <= 'b0;

// Generate "ref_ok_s2f2"

always @ ( posedge hclk or negedge hrstn )

if ( !hrstn )

ref_ok_s2f2 <= 'b0;

else

ref_ok_s2f2 <= ref_ok_s2f1;

// The "beg_region" will be set to "1" while "row_y_pic"

// reach the first row of the last 3 "1/4 region".

assign beg_region = ( 256 == row_y_pic || 512 == row_y_pic )

? 1'b1

: ( 768 == row_y_pic || 0 == row_y_pic)

? 1'b1

: 'b0;

// "refer_ok_hclk" will be set to "1" if "beg_region" while

// "count_1023_hclk" is active and "break" is inactive.

always @ ( posedge hclk_gt or negedge hrstn ) begin

if ( !hrstn )

refer_ok_hclk <= 'b0;

else begin

if ( !break ) begin

if ( beg_region && count_1023_hclk )

refer_ok_hclk <= 1'b1;

else

refer_ok_hclk <= 'b0;

end

else

refer_ok_hclk <= 'b0;

end

end

// Generate "ref_ok_f2s1"

always @ ( posedge ad_clk or negedge hrstn )

if ( !hrstn )

ref_ok_f2s1 <= 'b0;

else

if ( refer_ok_hclk )

ref_ok_f2s1 <= 1'b1;

else

ref_ok_f2s1 <= 'b0;

// Generate "ref_ok_f2s2" and "ref_ok_f2s3".

always @ ( posedge ad_clk or negedge hrstn )

if ( !hrstn )

{ ref_ok_f2s3, ref_ok_f2s2 } <= 2'b00;

else

{ ref_ok_f2s3, ref_ok_f2s2 } <= { ref_ok_f2s2, ref_ok_f2s1 };

// Generate "refer_ok"

always @ ( ref_ok_f2s3 or ref_ok_f2s2 )

case ( { ref_ok_f2s3, ref_ok_f2s2 } )

2'b01 : refer_ok = 1'b1;

default : refer_ok = 'b0;

endcase

/** v Generate "refer_ok" which is in-phase with "ad_clk" v **/

//---------------------------------------------------------------------

/********** ^ Generate "int_req" ^ **********/

// Generate "count_1023_hclk".

assign count_1023_hclk = ( count_1023_pic && !count_1023_pic_reg )

? 1'b1

: 'b0;

// "count_1023_pic_reg" is a circle later than "count_1023_pic"

always @ ( posedge hclk or negedge hrstn )

if( !hrstn )

count_1023_pic_reg <= 'b0;

else

count_1023_pic_reg <= count_1023_pic;

// "beg_region_reg"

always @ ( posedge hclk or negedge hrstn )

if ( !hrstn )

beg_region_reg <= 'b0;

else

beg_region_reg <= beg_region;

// Indicate the generation of "int_req" to CPU to read the row

// of "0", "256", "512" and "768".

always @ ( posedge hclk or negedge hrstn )

if ( !hrstn )

beg_region_index <= 'b0;

else if ( int_req_ref_ok )

beg_region_index <= 'b0;

else

if ( beg_region && !beg_region_reg )

beg_region_index <= 1'b1;

else

beg_region_index <= beg_region_index;

这个恐怕你要自己检查一下了,代码中没有简单的loop。你要检查一下生成的网表,他报的warning中给出了loop的路径,你检查一下是那条?自己分析一下。

嗯,我查看了一下那条路径,还没有去看网表。你这么一提醒,我明天去看看网表看看。非常感谢!有不明白的以后再多多请教了!