verilog反馈结构求助 折腾两星期了

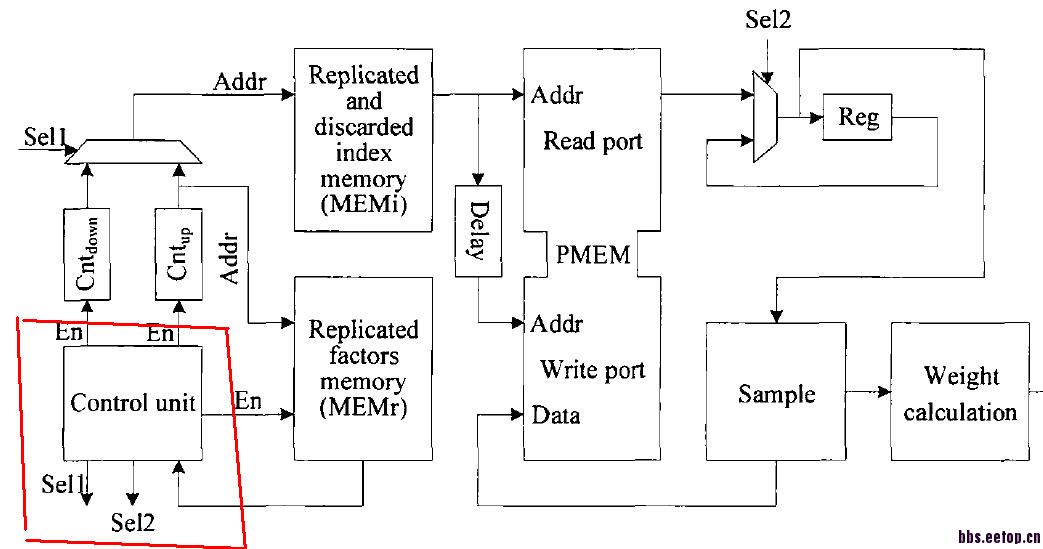

如上面的机构图,MEMr存储器存储(深度128)上半部分为大于0的整数,下半部分为0,所有数和为深度128,它是PMEM存储器对应数据需要复制的次数(这个复制次数对应的PMEM地址储存在MEMi存储器里)。次模块实现的关键就是控制单元的设计(图红线部分),从MEMr里依次取出数据,得到iMEM的地址信号。

比如MEMr第一个数据为4,则iMEM的地址信号依次为0,127,126,125(相当于把0号数据覆盖到最底层的位置)

再取出下一个MEMr数据2,则iMEM的地址信号依次为1,124,

再取出下一个MEMr数据1,则iMEM的地址信号依次为2,

再取出下一个MEMr数据3,则iMEM的地址信号依次为3,123,122,

。

求助:这个控制单元该怎么编写,参考的论文好像在控制单元里面用了一个递减计数器,好用的异步信号标记,开始时用一个时钟的启动脉冲来取出MEMr的第一个数,当MEMr数据为0时,整个模块停止。折腾很久了还是没搞出来,总是出问题。

问题出在那里,可以把波形或代码贴出来好帮你查看

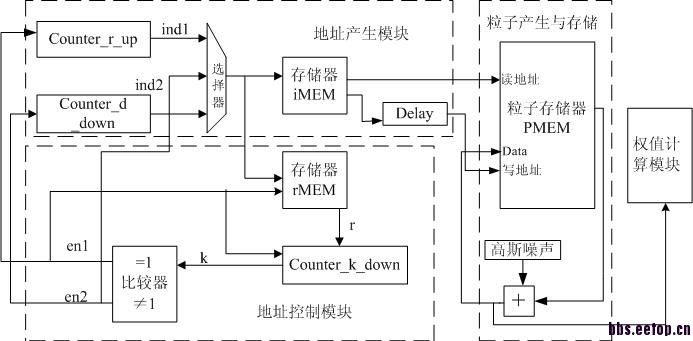

我是这样做的 ,先给一个启动脉冲pulse,启动en1信号从rMEM读出第一个数x后,先判断x是否大于1,如大于1,则把x-1送入k_down计数器,如等于1,则马上启动en1信号 读出rMEM下一个数

k_down计数器的输出k_out等于1时启动en1信号

en2信号基本就是en1的取反了。

以下是代码:

module sample1(clk,set,en1,en2,ena,pulse,r_up,d_down,r_out,k_out,addrb,wea,addra,dina

);

input clk,set,wea,pulse,ena;

input[6:0]addra,dina;

output [6:0]r_up,d_down,addrb,r_out(存储器输出),k_out;

output en1,en2,r_ready,down_en,up_en;

reg [6:0]r_up,d_down,addrb,k_out;

//counter_r_up

always@(posedge clk)

begin

if(set) begin

r_up<=0;

end

else if(en1==1)

begin

r_up<=r_up+1;

end

end

//counter_d_down

always@(posedge clk)

begin

if(set)

begin

d_down<=7'd127;

end

else if(en2==1)

begin

d_down<=d_down-1;

end

end

//选择器

always@(posedge clk)

begin

if(set)

begin

addrb<=0;

end

else if(en2==1)

begin

addrb<=d_down;

end

else

begin

addrb<=r_up;

end

end

//en1和en2信号赋值

assign en1=((r_out==1)||pulse||(k_out==1))?1:0;

assign en2=(r_out>1)&&(k_out!==1)&&(!pulse);

//counter_k_down #######感觉这部分有问题

always@(posedge clk)

begin

if(set)

begin

k_out<=0;

end

else if(en1==1)

begin

k_out<=r_out-1;

end

else if(en2==1)

begin

k_out<=k_out-1;

end

end

//rMEM 存储器例化

rMEM MYrMEM (

.clka(clk), // input clka

.ena(ena), // input ena

.wea(wea), // input [0 : 0] wea

.addra(addra), // input [6 : 0] addra

.dina(dina), // input [6 : 0] dina

.clkb(clk), // input c // input [6 : 0] addra

.rstb(set), // input rstb

.enb(en1), // input enb

.addrb(addrb), // input [6 : 0] addrb

.doutb(r_out) // output [6 : 0] doutb

);

endmodul

这里的en1、en2信号该用时序还是逻辑的?有些做成时序的可以延时

已重新发了个贴,希望帮忙,非常感谢