Active-HDL 是前仿真吗?

时间:10-02

整理:3721RD

点击:

写了一个程序,代码如下:

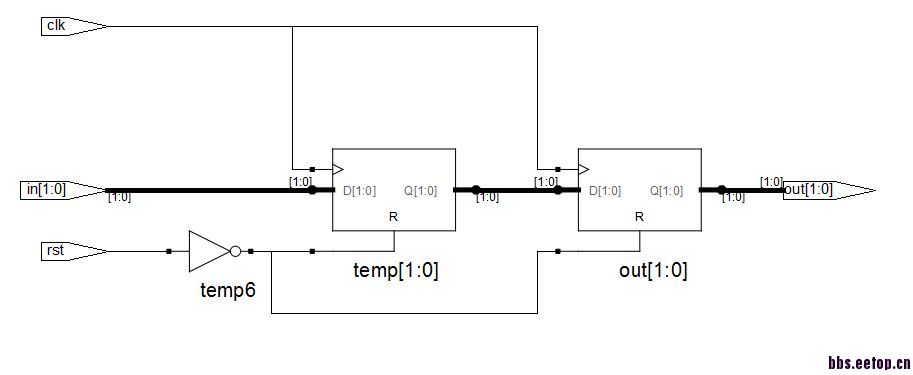

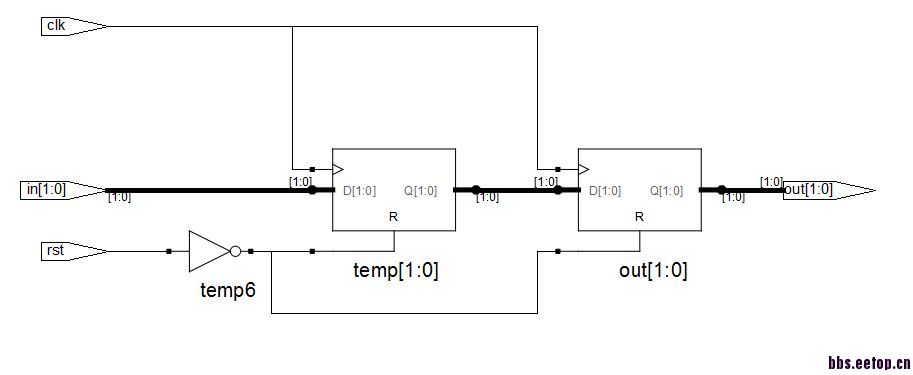

经过综合,RTL图如下:

可见out和temp的赋值是同时进行的,没有先后顺序,若使用非阻塞型的赋值,情况也是如此;

用Active-HDL的testbench进行仿真,代码如下:

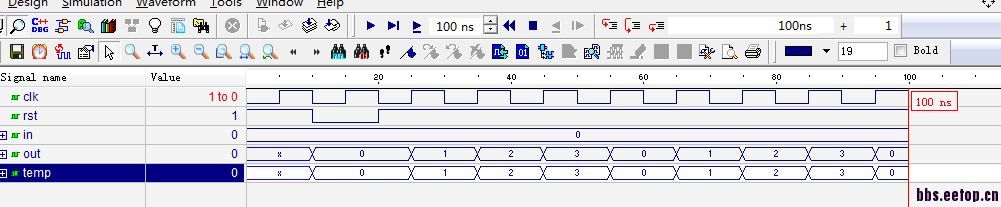

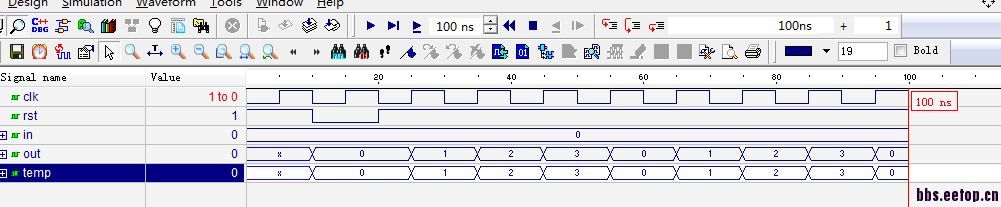

仿真结果时序图如下:

out和temp是同步进行输出,所以我判断改仿真为前仿真,没有考虑D触发器的计算时间。

- //在两个进程中进行阻塞赋值,观察时候有先后顺序;并观察testbench的结果,以判断testbench是前仿还是后仿

- module test9(clk,rst,in,temp,out);

- input clk,rst;

- input [1:0] in;

- output reg [1:0] out;

- output reg [1:0] temp;

- always @(posedge clk or negedge rst)

- if(!rst)

- temp=in;

- else

- temp=temp+1;

- always @(posedge clk or negedge rst)

- if(!rst)

- out=0;

- else

- out=temp;

- endmodule

经过综合,RTL图如下:

可见out和temp的赋值是同时进行的,没有先后顺序,若使用非阻塞型的赋值,情况也是如此;

用Active-HDL的testbench进行仿真,代码如下:

- //-----------------------------------------------------------------------------

- //

- // Title : test9_1

- // Design : test9

- // Author :

- // Company :

- //

- //-----------------------------------------------------------------------------

- //

- // File : test9_1.v

- // Generated : Fri May 17 10:59:29 2013

- // From : interface description file

- // By : Itf2Vhdl ver. 1.22

- //

- //-----------------------------------------------------------------------------

- //

- // Description :

- //

- //-----------------------------------------------------------------------------

- `timescale 1 ns / 1 ps

- //{{ Section below this comment is automatically maintained

- // and may be overwritten

- //{module {test9_1}}

- module test9_1 ();

- //}} End of automatically maintained section

- // -- Enter your statements here -- //

- reg clk,rst;

- reg [1:0] in;

- wire [1:0] out,temp;

- initial

- begin

- rst=1;

- #10 rst=0;

- #10 rst=1;

- end

- initial

- clk=0;

- always

- #5 clk=~clk;

- initial

- in=0;

-

- test9 cc(clk,rst,in,temp,out);

- endmodule

- //在两个进程中进行阻塞赋值,观察时候有先后顺序;并观察testbench的结果,以判断testbench是前仿还是后仿

- module test9(clk,rst,in,temp,out);

- input clk,rst;

- input [1:0] in;

- output reg [1:0] out;

- output reg [1:0] temp;

- always @(posedge clk or negedge rst)

- if(!rst)

- temp=in;

- else

- temp=temp+1;

- always @(posedge clk or negedge rst)

- if(!rst)

- out=0;

- else

- out=temp;

- endmodule

仿真结果时序图如下:

out和temp是同步进行输出,所以我判断改仿真为前仿真,没有考虑D触发器的计算时间。