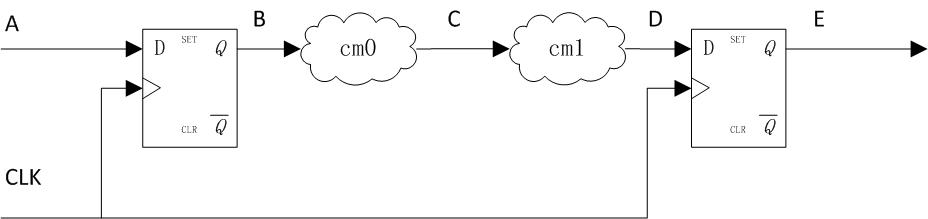

一道ASIC设计笔试题,求大神

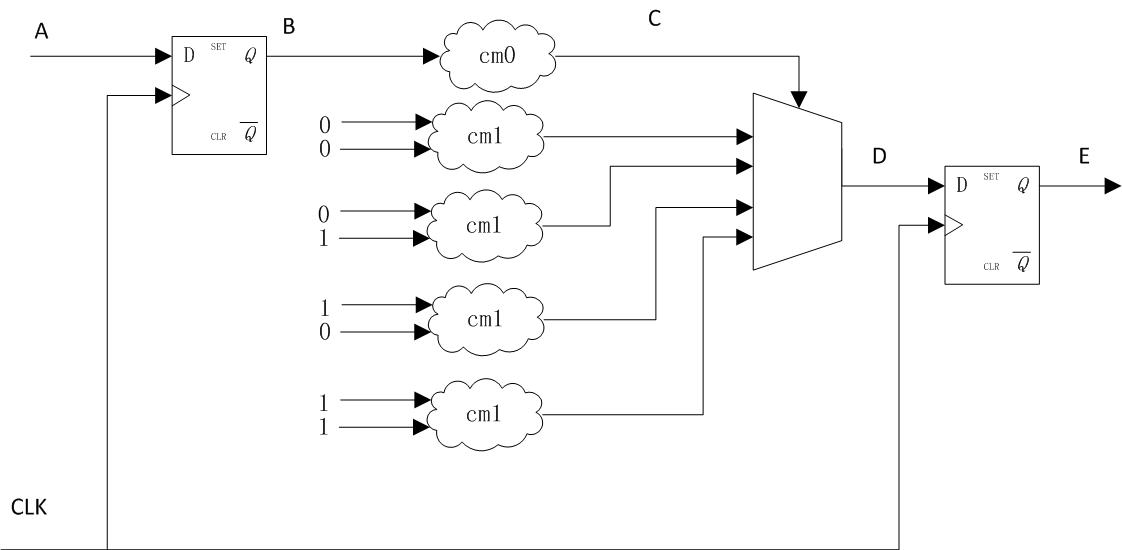

放置4个cm1,分别用定值00、01、10、11作为输入,在D前放置4-to-1 Mux,将cm0输出作为选择信号。

这样做为了什么?优化cm1吗?

将cm1的7ns替换为Mux Cell的延时

我懂了,因为C是2bit,所以将cm1复用的话,可以把cm1从路径中拿走,因为cm0输出一旦确定,cm1的输出就同样确定了,不需要每次都因为cm0的变换而重新输出。这个方法实在是太棒了!

谢谢你!

,不错不错

真是大牛啊

正解,牛人哈。

学习学习,不是很懂

我也想到了,这些其实还是要多看看资料,很多外文书籍中都有的。

这个是个想法的问题。看了提示以后就豁然开朗了。1bit->2bits->1bit,很明显可以做简化处理。

有没有比较好的书推荐一下啊,我刚刚学,想找些书看看

我还是基本功太差了 一直都是写HDL 基础真不扎实啊

请问你这个图是用什么工具画的?

visio啊

我还是觉得用visio画不方便

visio有这种现成的库么

那应该用什么画?我不太清楚唉,感觉基本数字电路的符号visio都有……

好东西!

Nvidia的笔试题目是吧

题目中并没有说明MUX的延迟,这个你怎么确保满足100MHZ的时钟?

记得DC的优化思想里面有讲,这个应该属于逻辑复制,印象中是个加法器的例子。

应该还有其他方法,比如如果前一级或者后一级path有空余,可以挪动逻辑来实现;

在后端时,也可以挪到clock来实现。但是,原则是越靠近前期对应好,效果越好,风险越小。

面积换速度的典型案例!

不错的一道题,赞一个!

面积换速度牛牛牛

把cm0挪到第一个D触发器之前不是更简单直接么?

我当时笔试的时候就只这么干的,应该是华丽丽的被鄙视啦

这样子 肯定不行啊………………

cm0移到第一级之前 或者 cm1移到第二级之后也是一个处理办法。

从这个题目的提示来看,因为C为2bit,cm1移到第二级之后,这样第二级D触发器改为2个,正好把2bit的C打一拍。

5楼的方案增加了一个4选一的mux并增加了3x的cm1,这个方案只增加了1bit D触发器。

假如电路允许的话,应该是移动cm1的方案更好。