大学生作业 串行检测器 门级仿真波形出错

时间:10-02

整理:3721RD

点击:

我们的实验报告要求写一个串行检测器 当检测到1111四个1或者超过4个1以上的数列时就输出1 否则就输出0

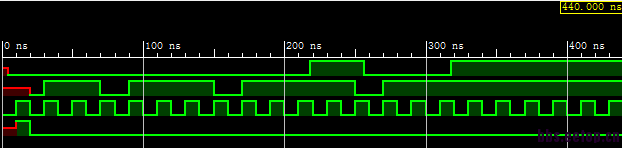

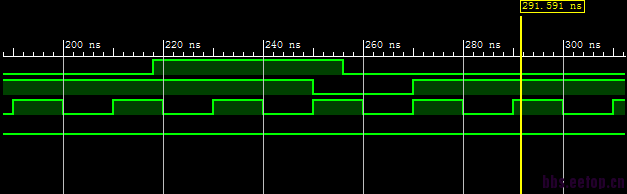

图像中行为级4个1开始输出1 而门级三个1就开始输出1了 而且门级有延时 大概是7.85ns

因为我的确是初学者 所以很多东西真的不懂 还有望各位高手细心指点 小弟心存感激

(如果有人指点 需要的我我可以上传report)

图像中行为级4个1开始输出1 而门级三个1就开始输出1了 而且门级有延时 大概是7.85ns

因为我的确是初学者 所以很多东西真的不懂 还有望各位高手细心指点 小弟心存感激

(如果有人指点 需要的我我可以上传report)

- 2,verilog代码

- module Check1111(data,clk,clear,result);

-

- input data,clk,clear; //输入信号data,时钟clk,复位信号clear

- output result; //输出信号result

- reg x,result; //变量寄存器x,输出变量寄存器result

- reg [1:0] state; //二位状态寄存器

- reg [1:0] next_state; //二位下一刻状态寄存器

-

- parameter S0=2'b00, //为状态机的四个状态编码

- S1=2'b01,

- S2=2'b10,

- S3=2'b11;

-

- always@(posedge clk or posedge clear)

- if(clear)

- state <= S0; //复位信号到来 状态赋值到SO初始状态

- else

- state <= next_state; //时钟信号到来 将下一刻的状态赋值到当前状态

-

- always@(state or data) //状态或数据流变化时

-

- x = data; //将data赋值到寄存器x

-

- always@(state or x) //状态或寄存器x变化时

- begin

-

- case(state)

- S0 : if(x==1)

- begin //若x检测到1,跳到状态S1,result输出0

- next_state = S1;

- result=0;

- end

-

- else

- begin //若x检测到0,跳到状态S0,result输出0

- next_state = S0;

- result=0;

- end

-

- S1 : if(x==1)

- begin //若x检测到1,跳到状态S2,result输出0

- next_state = S2;

- result=0;

- end

-

- else

- begin

- next_state = S0; //若x检测到0,跳到状态S0,result输出0

- result=0;

- end

-

- S2 : if(x==1)

- begin //若x检测到1,跳到状态S3,result输出0

- next_state = S3;

- result=0;

- end

-

- else

- begin //若x检测到0,跳到状态S0,result输出0

- next_state = S0;

- result=0;

- end

-

- S3 : if(x==1)

- begin //若x检测到1,跳到状态S3,result输出1

- next_state = S3;

- result=1;

- end

-

- else

- begin //若x检测到0,跳到状态S0,result输出0

- next_state = S0;

- result=0;

- end

- default : next_state = S0; //默认的状态为S0

- endcase

- end

-

- endmodule

- 3,仿真代码

- `timescale 1ns / 1ps

- module test_for_check1111;

- // Inputs

- reg data;

- reg clk;

- reg clear;

- // Outputs

- wire result;

- // Instantiate the Unit Under Test (UUT)

- Check1111 uut (

- .data(data),

- .clk(clk),

- .clear(clear),

- .result(result)

- );

- initial

- begin

- // Initialize Inputs

- data = 0; //信号赋初值

- clk = 0;

- clear = 0;

-

- forever #100 clk = ~clk; //设置一个5M时钟

-

- end

-

- initial

- begin

- #50 clear = ~clear; //在开始的时候复位端有效一次使电路赋初值

- #50 clear = ~clear;

-

- @(posedge clk)data = 1; //在时钟上升沿到来的时候提供一段数据流

- @(posedge clk)data = 1;

- @(posedge clk)data = 1;

- @(posedge clk)data = 1;

- @(posedge clk)data = 1;

- @(posedge clk)data = 1;

- @(posedge clk)data = 1;

- @(posedge clk)data = 0;

- @(posedge clk)data = 1;

- @(posedge clk)data = 1;

- @(posedge clk)data = 1;

- @(posedge clk)data = 0;

-

- $stop;

- end

-

- endmodule

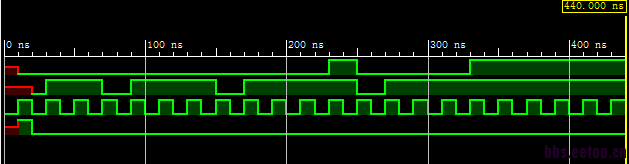

行为级仿真

门级仿真

门级仿真的延时

难道就没人帮助一下吗T^T

状态机编码建议使用one-hot编码

即:

S1 = 0001

S2 = 0010

S3 = 0100

S4 = 1000

然后你正好可以吧S4的最高位作为输出~用一段式可能好点这里

可以试下用移位寄存器做

reg [3:0] a;

a <= {din, a[3:1]}

wire result = (a==4'hf);1.截图不截信号名称.......谁知道什么是什么......

2.截图和代码对不上.........你5m的时钟在哪里,只看到一个周期20ns的东西不知道是什么......你两个50ns的clear自反复位在哪里?只看到一个10ns的X和一个10ns的脉冲.....

在逻辑上,仿真结果与你的代码是符合的,没问题

state进入s3状态,到result输出是组合逻辑,必然少一个节拍

既然自称初学,用不好二段式的组合逻辑开节点,还是先老老实实先换一三段吧...........

支持这个方法,简单直接6L的是不错