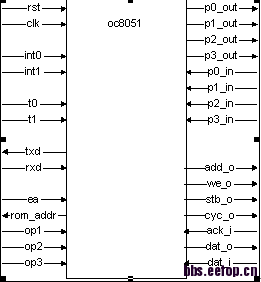

oc8051

opencore上下载的oc8051代码,想把这个搞到fpga中试试,把p0_in直接指定给开关,p0_out指定给led,想通过开关简单的实现一下p0口的I/O特性,但是程序写进去之后,led常亮,开关不起作用。求解释!

至少要有个rom,在里面放程序的吧

想着先直接指定FPGA专用引脚试试,这步也要用到用rom?

嗯,你是对的,我先定制一个ram再试试!

建议先仿真,仿真了没问题再放到板子上跑

嗯,正在研究中~

你把p0_in连接到开关上,p0_out连接到LED灯上是不对的,正确的做法是例化一个IO,把p0_in接到IO的接受端,p0_out接到IO的发送端,IO的OE端用p0_out控制(保证当p0_out为1时,IO中的三态门打开)

其他的IO用同样的接法

嗯,你说的有道理。不过这样的话就远离了我的本意,我是想在FPGA 板上验证一下8051内核。

再看到 assign p0_data = rmw ? p0_out : p0_in;证实了我先前的p0_in控制p0_out的想法是错误的。

其实真正的8051芯片外部的pin都是用这种方法接的,不会把p0_in p0_out都拉到IO上的。

嗯,代码正在研习~

open core上面的8051貌似有很多问题,我也是下载下来自己仿写的代码,仿真才发现很多问题!

嗯,逐个模块调试!

前段时间搞过oc8051,源代码的仿真可以过, 但是放进FPGA里面要重新例化altera的ROM和RAM,接口时序跟这个wishbone不一样,没搞出来。可以交流交流,email:tobemyselfchina@foxmail.com

想请教大虾,这个oc8051你仿过没有的?小弟用oc8051自带的ROM仿真模型仿真的时候可以过,但是用altera例化的ROM就过不了,接口时序的问题,请教一下你!

我正在给OC8051增加调试模块,和Keil联合调试MCU

http://bbs.eetop.cn/thread-390441-1-1.html

能跑仿真吗?