一个verilog题目

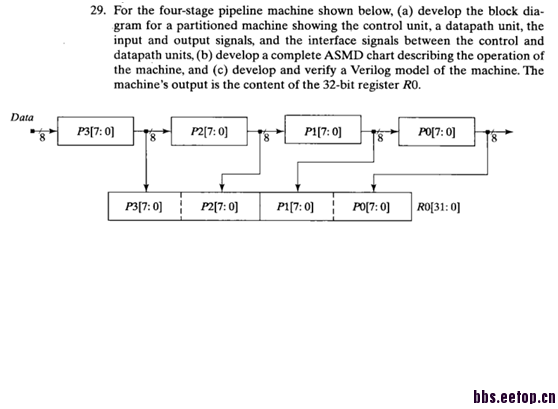

此题是课后作业,不知道从何下手,信号定义除了8位的输入信号,32位的输出信号,时钟信号,还有什么呢?请教对数字设计比较熟练的人解答。

此题是课后作业,不知道从何下手,信号定义除了8位的输入信号,32位的输出信号,时钟信号,还有什么呢?请教对数字设计比较熟练的人解答。

uestc,窦衡老师的作业?

。

module serial2parallel(

input i_clk ,

input i_rst_n,

input [7:0] datain,

output reg [31:0] dataout,

output reg dvldout

);

reg [7:0] rshiftreg1 ;

reg [7:0] rshiftreg2 ;

reg [7:0] rshiftreg3 ;

reg [7:0] rshiftreg4;

reg [1:0] rcnt ;

always @(posedge i_clk or negedge i_rst_n)

begin

if(!i_rst_n)

rcnt <= 2'b00;

else

rcnt <= rcnt +2'd1;

end

always @(posedge i_clk or negedge i_rst_n)

begin

if(!i_rst_n)

begin

rshiftreg1 <= 8'h00 ;

rshiftreg2 <= 8'h00 ;

rshiftreg3 <= 8'h00 ;

rshiftreg4 <= 8'h00 ;

end

else

rshiftreg1 <= datain;

rshiftreg2 <= rshiftreg1 ;

rshiftreg3 <= rshiftreg2 ;

rshiftreg4 <= rshiftreg3 ;

end

always @(posedge i_clk or negedge i_rst_n)

begin

if(!i_rst_n)

begin

dataout <= 32'd0;

dvldout <= 1'b0 ;

end

else(rcnt==2'b11)

begin

dataout <= {rshiftreg1,rshiftreg2,rshiftreg3,rshiftreg4};

dvldout <= 1'b1 ;

end

else

begin

dataout <= 32'd0;

dvldout <= 1'b0 ;

end

end