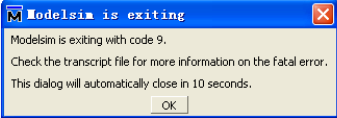

求助:modelsim 仿真时加波形信号之前出现 #symInitialize后面是乱码

然后加波形信号时会出现错误

transcript窗口显示内存和转换空间不足的信息,但是我看需要分配的字节空间也不多啊,不知道是怎么回事。

这个问题困扰了我好多天了,希望大侠们能帮帮我,谢谢!

如果你确实想解决问题,我觉得你还是把testbench上传吧。

你好,我是仿真ise生成的aurora ip核,用的是里面的testbench,没有修改过,以前仿真是没有问题的,所以我觉得是modelsim的某些设置问题吧?像symInitialize是跟什么有关呢?

`timescale 1 ns / 1 ps

module aurora_4byte_16lane_TB;

//*************************Parameter Declarations**************************

parameter SIM_MAX_TIME = 525000; //To quit the simulation

//156.25MHz GT Reference clock

parameter CLOCKPERIOD_1 = 6.4;

parameter CLOCKPERIOD_2 = 6.4;

parameter LATENCY0 = 0;

parameter LATENCY1 = 0;

parameter LATENCY2 = 0;

parameter LATENCY3 = 0;

parameter LATENCY4 = 0;

parameter LATENCY5 = 0;

parameter LATENCY6 = 0;

parameter LATENCY7 = 0;

parameter LATENCY8 = 0;

parameter LATENCY9 = 0;

parameter LATENCY10 = 0;

parameter LATENCY11 = 0;

parameter LATENCY12 = 0;

parameter LATENCY13 = 0;

parameter LATENCY14 = 0;

parameter LATENCY15 = 0;

//************************Internal Register Declarations*****************************

//Freerunning Clock

reg reference_clk_1_n_r;

reg reference_clk_2_n_r;

//Global signals

reg gsr_r;

reg gts_r;

reg reset_i;

//********************************Wire Declarations**********************************

//Freerunning Clock

wire reference_clk_1_p_r;

wire reference_clk_2_p_r;

//Dut1

//Error Detection Interface

wire hard_err_1_i;

wire soft_err_1_i;

wire frame_err_1_i;

//Status

wire channel_up_1_i;

wire [0:15] lane_up_1_i;

//GT Serial I/O

wire [0:15] rxp_1_i;

wire [0:15] rxn_1_i;

wire [0:15] txp_1_i;

wire [0:15] txn_1_i;

// Error signals from the Local Link packet checker

wire [0:7] err_count_1_i;

//Dut2

//Error Detection Interface

wire hard_err_2_i;

wire soft_err_2_i;

wire frame_err_2_i;

//Status

wire channel_up_2_i;

wire [0:15] lane_up_2_i;

//GT Serial I/O

wire [0:15] rxp_2_i;

wire [0:15] rxn_2_i;

wire [0:15] txp_2_i;

wire [0:15] txn_2_i;

// Error signals from the Local Link packet checker

wire [0:7] err_count_2_i;

//*********************************Main Body of Code**********************************

//_________________________Serial Connections________________

assign #LATENCY0 rxp_1_i[0] = txp_2_i[0];

assign #LATENCY0 rxn_1_i[0] = txn_2_i[0];

assign #LATENCY0 rxp_2_i[0] = txp_1_i[0];

assign #LATENCY0 rxn_2_i[0] = txn_1_i[0];

assign #LATENCY1 rxp_1_i[1] = txp_2_i[1];

assign #LATENCY1 rxn_1_i[1] = txn_2_i[1];

assign #LATENCY1 rxp_2_i[1] = txp_1_i[1];

assign #LATENCY1 rxn_2_i[1] = txn_1_i[1];

assign #LATENCY2 rxp_1_i[2] = txp_2_i[2];

assign #LATENCY2 rxn_1_i[2] = txn_2_i[2];

assign #LATENCY2 rxp_2_i[2] = txp_1_i[2];

assign #LATENCY2 rxn_2_i[2] = txn_1_i[2];

assign #LATENCY3 rxp_1_i[3] = txp_2_i[3];

assign #LATENCY3 rxn_1_i[3] = txn_2_i[3];

assign #LATENCY3 rxp_2_i[3] = txp_1_i[3];

assign #LATENCY3 rxn_2_i[3] = txn_1_i[3];

assign #LATENCY4 rxp_1_i[4] = txp_2_i[4];

assign #LATENCY4 rxn_1_i[4] = txn_2_i[4];

assign #LATENCY4 rxp_2_i[4] = txp_1_i[4];

assign #LATENCY4 rxn_2_i[4] = txn_1_i[4];

assign #LATENCY5 rxp_1_i[5] = txp_2_i[5];

assign #LATENCY5 rxn_1_i[5] = txn_2_i[5];

assign #LATENCY5 rxp_2_i[5] = txp_1_i[5];

assign #LATENCY5 rxn_2_i[5] = txn_1_i[5];

assign #LATENCY6 rxp_1_i[6] = txp_2_i[6];

assign #LATENCY6 rxn_1_i[6] = txn_2_i[6];

assign #LATENCY6 rxp_2_i[6] = txp_1_i[6];

assign #LATENCY6 rxn_2_i[6] = txn_1_i[6];

assign #LATENCY7 rxp_1_i[7] = txp_2_i[7];

assign #LATENCY7 rxn_1_i[7] = txn_2_i[7];

assign #LATENCY7 rxp_2_i[7] = txp_1_i[7];

assign #LATENCY7 rxn_2_i[7] = txn_1_i[7];

assign #LATENCY8 rxp_1_i[8] = txp_2_i[8];

assign #LATENCY8 rxn_1_i[8] = txn_2_i[8];

assign #LATENCY8 rxp_2_i[8] = txp_1_i[8];

assign #LATENCY8 rxn_2_i[8] = txn_1_i[8];

assign #LATENCY9 rxp_1_i[9] = txp_2_i[9];

assign #LATENCY9 rxn_1_i[9] = txn_2_i[9];

assign #LATENCY9 rxp_2_i[9] = txp_1_i[9];

assign #LATENCY9 rxn_2_i[9] = txn_1_i[9];

assign #LATENCY10 rxp_1_i[10] = txp_2_i[10];

assign #LATENCY10 rxn_1_i[10] = txn_2_i[10];

assign #LATENCY10 rxp_2_i[10] = txp_1_i[10];

assign #LATENCY10 rxn_2_i[10] = txn_1_i[10];

assign #LATENCY11 rxp_1_i[11] = txp_2_i[11];

assign #LATENCY11 rxn_1_i[11] = txn_2_i[11];

assign #LATENCY11 rxp_2_i[11] = txp_1_i[11];

assign #LATENCY11 rxn_2_i[11] = txn_1_i[11];

assign #LATENCY12 rxp_1_i[12] = txp_2_i[12];

assign #LATENCY12 rxn_1_i[12] = txn_2_i[12];

assign #LATENCY12 rxp_2_i[12] = txp_1_i[12];

assign #LATENCY12 rxn_2_i[12] = txn_1_i[12];

assign #LATENCY13 rxp_1_i[13] = txp_2_i[13];

assign #LATENCY13 rxn_1_i[13] = txn_2_i[13];

assign #LATENCY13 rxp_2_i[13] = txp_1_i[13];

assign #LATENCY13 rxn_2_i[13] = txn_1_i[13];

assign #LATENCY14 rxp_1_i[14] = txp_2_i[14];

assign #LATENCY14 rxn_1_i[14] = txn_2_i[14];

assign #LATENCY14 rxp_2_i[14] = txp_1_i[14];

assign #LATENCY14 rxn_2_i[14] = txn_1_i[14];

assign #LATENCY15 rxp_1_i[15] = txp_2_i[15];

assign #LATENCY15 rxn_1_i[15] = txn_2_i[15];

assign #LATENCY15 rxp_2_i[15] = txp_1_i[15];

assign #LATENCY15 rxn_2_i[15] = txn_1_i[15];

//__________________________Global Signals_____________________________

//Simultate the global reset that occurs after configuration at the beginning

//of the simulation. Note that both GT smart models use the same global signals.

assign glbl.GSR = gsr_r;

assign glbl.GTS = gts_r;

initial

begin

gts_r = 1'b0;

gsr_r = 1'b1;

#(16*CLOCKPERIOD_1);

gsr_r = 1'b0;

end

//____________________________Clocks____________________________

initial

reference_clk_1_n_r = 1'b0;

always

#(CLOCKPERIOD_1 / 2) reference_clk_1_n_r = !reference_clk_1_n_r;

assign reference_clk_1_p_r = !reference_clk_1_n_r;

initial

reference_clk_2_n_r = 1'b0;

always

#(CLOCKPERIOD_2 / 2) reference_clk_2_n_r = !reference_clk_2_n_r;

assign reference_clk_2_p_r = !reference_clk_2_n_r;

//____________________________Resets____________________________

initial

begin

reset_i = 1'b1;

#200 reset_i = 1'b0;

end

//________________________Instantiate Dut 1 ________________

aurora_4byte_16lane_exdes example_design_1_i

(

// User IO

.RESET(reset_i),

// Error signals from Aurora

.HARD_ERR(hard_err_1_i),

.SOFT_ERR(soft_err_1_i),

.FRAME_ERR((frame_err_1_i)),

// Status Signals

.LANE_UP(lane_up_1_i),

.CHANNEL_UP(channel_up_1_i),

.INIT_CLK_P(reference_clk_1_p_r),

.INIT_CLK_N(reference_clk_1_n_r),

.GT_RESET_IN(gsr_r),

// Clock Signals

.GTXQ0_P(reference_clk_1_p_r),

.GTXQ0_N(reference_clk_1_n_r),

.GTXQ2_P(reference_clk_1_p_r),

.GTXQ2_N(reference_clk_1_n_r),

// GT I/O

.RXP(rxp_1_i),

.RXN(rxn_1_i),

.TXP(txp_1_i),

.TXN(txn_1_i),

// Error signals from the Local Link packet checker

.ERR_COUNT(err_count_1_i)

);

//________________________Instantiate Dut 2 ________________

aurora_4byte_16lane_exdes example_design_2_i

(

// User IO

.RESET(reset_i),

// Error signals from Aurora

.HARD_ERR(hard_err_2_i),

.SOFT_ERR(soft_err_2_i),

.FRAME_ERR((frame_err_2_i)),

// Status Signals

.LANE_UP(lane_up_2_i),

.CHANNEL_UP(channel_up_2_i),

.INIT_CLK_P(reference_clk_2_p_r),

.INIT_CLK_N(reference_clk_2_n_r),

.GT_RESET_IN(gsr_r),

// Clock Signals

.GTXQ0_P(reference_clk_2_p_r),

.GTXQ0_N(reference_clk_2_n_r),

.GTXQ2_P(reference_clk_2_p_r),

.GTXQ2_N(reference_clk_2_n_r),

// GT I/O

.RXP(rxp_2_i),

.RXN(rxn_2_i),

.TXP(txp_2_i),

.TXN(txn_2_i),

// Error signals from the Local Link packet checker

.ERR_COUNT(err_count_2_i)

);

always @ (posedge channel_up_1_i or posedge channel_up_2_i)

begin

if((channel_up_1_i == 1'b1) && (channel_up_2_i == 1'b1))

begin

$display("\nAURORA_TB : INFO : @Time : %t CHANNEL_UP is asserted in both DUT\n", $time);

#5000 $display("\nAURORA_TB : INFO : TEST PASS\n");

$finish;

end

end

always @ (posedge err_count_1_i[7] or posedge err_count_2_i[7])

begin

if((err_count_1_i >= 8'b0000_0001) || (err_count_2_i >= 8'b0000_0001))

begin

$display("\nAURORA_TB : ERROR : TEST FAIL\n");

$display("\nAURORA_TB : INFO : ERR_COUNT1 = %b ERR_COUNT2 = %b\n",err_count_1_i,err_count_2_i);

#1000 $display("AURORA_TB : INFO : Exiting from simulation ....\n");

$finish;

end

end

//Abort the simulation when it reaches to max time limit

initial

begin

#(SIM_MAX_TIME) $display("\nAURORA_TB : INFO : Reached max. simulation time limit\n");

$finish;

end

endmodule各位大哥,请求有知道的吗,知道的不吝赐教

是啥问题?