逻辑电平检测电路

时间:10-02

整理:3721RD

点击:

最近在做一款芯片,里面需要用到这样一个电路(暂且命名为逻辑电平检测电路):

1、输出寄存器是由8位数据位(经过异或操作)和一位反转位组成的9位寄存器

2、反转位定义:当数据位里面有超过4位的1时,反转位设置为1,否则保持为0

3、输出的8位数据位要和反转位进行异或操作,然后才能输出

如何检测1的个数是否大于4的电路最好能用组合电路实现。

希望能有朋友指点一下,多谢了。

1、输出寄存器是由8位数据位(经过异或操作)和一位反转位组成的9位寄存器

2、反转位定义:当数据位里面有超过4位的1时,反转位设置为1,否则保持为0

3、输出的8位数据位要和反转位进行异或操作,然后才能输出

如何检测1的个数是否大于4的电路最好能用组合电路实现。

希望能有朋友指点一下,多谢了。

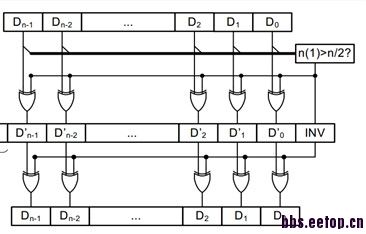

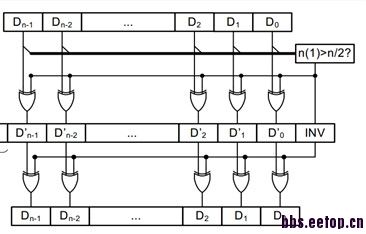

这个还是很 简单的,以前纯手工设计过这个电路 ,给你个思路

先把8为分成 两个4位;

然后设计组合逻辑:统计 4个输入中1的个数 产生的结果为 两bit的输出

然后 两位输出 + 另外的两位输出 = 3位的结果

这三位中最高位为1 则表示8位中有>=4的1 出现

问题已经搞定了,我用半加器的思路将8bit数进行相邻位半加操作,与的结果代表了2位1,异或的结果代表了1位1,这样再将四个与的结果进行半加,这样它的1位与代表4位1,这样就产生了1,2,4三种组合,然后再进行排列就可以了。

我还是很感谢你的回复,谢了。

这种发帖加自我结贴不超过1天的帖子还是慎重发出吧......

自己先思考下,实在没头绪再发吧....

这帖子里面的问题我想了三四天才发出来的,你要是有什么的好的实现方法可以发出来供大家看看,至于你的言下之意,阁下自己请用吧。

( ("000"&D0) + D1 + D2 +...+ D7 )>=4? 1:0;

看看,学习