verilog实现乘法器的代码,其中有一段不理解,大家帮忙看下,谢谢啦~~

时间:10-02

整理:3721RD

点击:

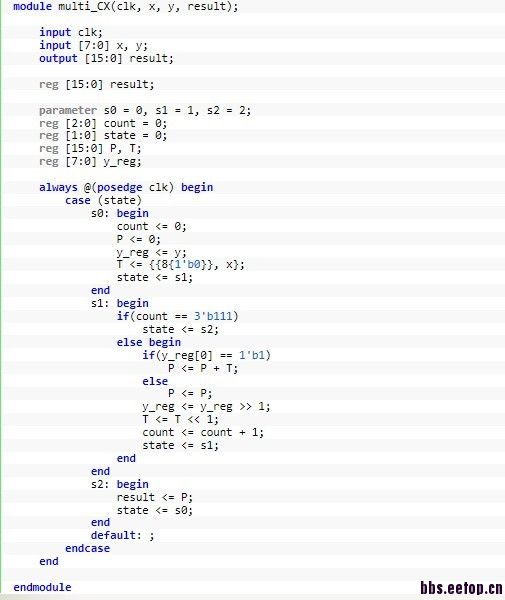

大家好,下面一段代码是实现2个8位数相乘的运算

module multi(clk , x , y , result);

input clk;

input [7:0]x , y;

output result;

reg [15:0]result;

parameter s0 = 0;

parameter s1 = 1;

parameter s2 = 2;

reg [2:0]count = 0;

reg [2:0]state = 0;

reg [15:0]P , T;

reg [7:0]y_reg;

always@(posedge clk)

begin

case(state)

s0:begin

count <=3'd0;

P<=16'b0;

y_reg<=y;

T<={{8{1'b0}} , x};

state<=s1;

end

s1:begin

if(count == 3'b111)

state<=s2;

else begin

if(y_reg[0] == 1'b1)

P<=P+T;

else

P<=P;

y_reg<=y_reg>>1;

T<=T<<1;

count<=count+1;

state<=s1;

end

end

s2:begin

result<=P;

state<=s0;

end

default:;

endcase

end

endmodule

其中:

else

P<=P;

y_reg<=y_reg>>1;

T<=T<<1;

count<=count+1;

state<=s1;

这个条件分支通过modelsim仿真发现,每个时钟都会有移位、计数器加1的操作,按我的思路,当if(y_reg[0] == 1'b1)成立时,下面的else分支应该永远不会实现的呀,这是怎么回事呢,请各位哥哥姐姐帮忙解答一下呗,谢谢了

这个清楚点,刚才那段代码没高亮,会的帮个忙,谢谢!

module multi(clk , x , y , result);

input clk;

input [7:0]x , y;

output result;

reg [15:0]result;

parameter s0 = 0;

parameter s1 = 1;

parameter s2 = 2;

reg [2:0]count = 0;

reg [2:0]state = 0;

reg [15:0]P , T;

reg [7:0]y_reg;

always@(posedge clk)

begin

case(state)

s0:begin

count <=3'd0;

P<=16'b0;

y_reg<=y;

T<={{8{1'b0}} , x};

state<=s1;

end

s1:begin

if(count == 3'b111)

state<=s2;

else begin

if(y_reg[0] == 1'b1)

P<=P+T;

else

P<=P;

y_reg<=y_reg>>1;

T<=T<<1;

count<=count+1;

state<=s1;

end

end

s2:begin

result<=P;

state<=s0;

end

default:;

endcase

end

endmodule

其中:

else

P<=P;

y_reg<=y_reg>>1;

T<=T<<1;

count<=count+1;

state<=s1;

这个条件分支通过modelsim仿真发现,每个时钟都会有移位、计数器加1的操作,按我的思路,当if(y_reg[0] == 1'b1)成立时,下面的else分支应该永远不会实现的呀,这是怎么回事呢,请各位哥哥姐姐帮忙解答一下呗,谢谢了

这个清楚点,刚才那段代码没高亮,会的帮个忙,谢谢!

这里的else只管 P<=P; 这一句

嗯嗯,刚才突然发现这个问题了,else下面没有begin end,所以只管P<=P一句; 谢谢啦 O(∩_∩)O~