关于Cyclone II EP2C5 的 FIFO 问题

时间:10-02

整理:3721RD

点击:

Hi,

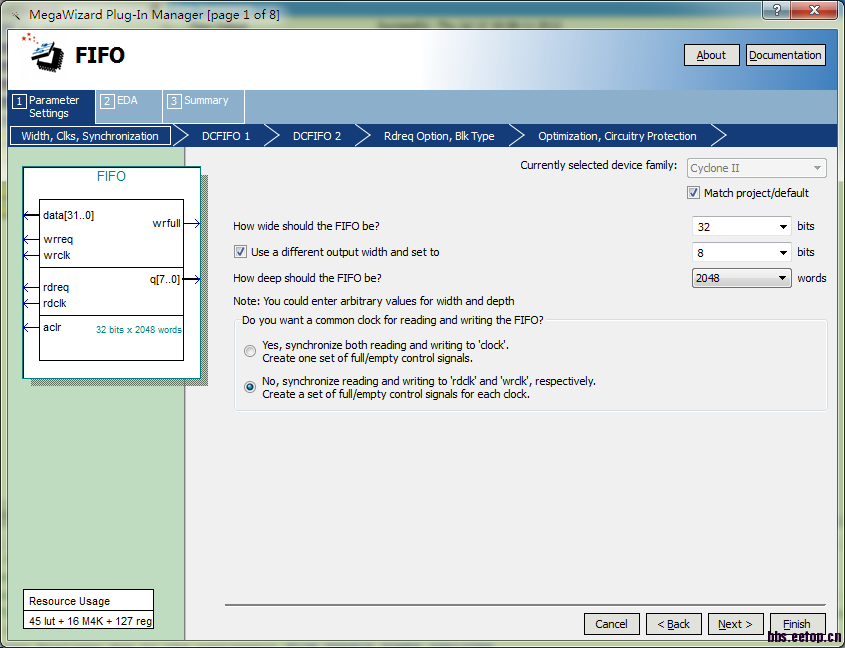

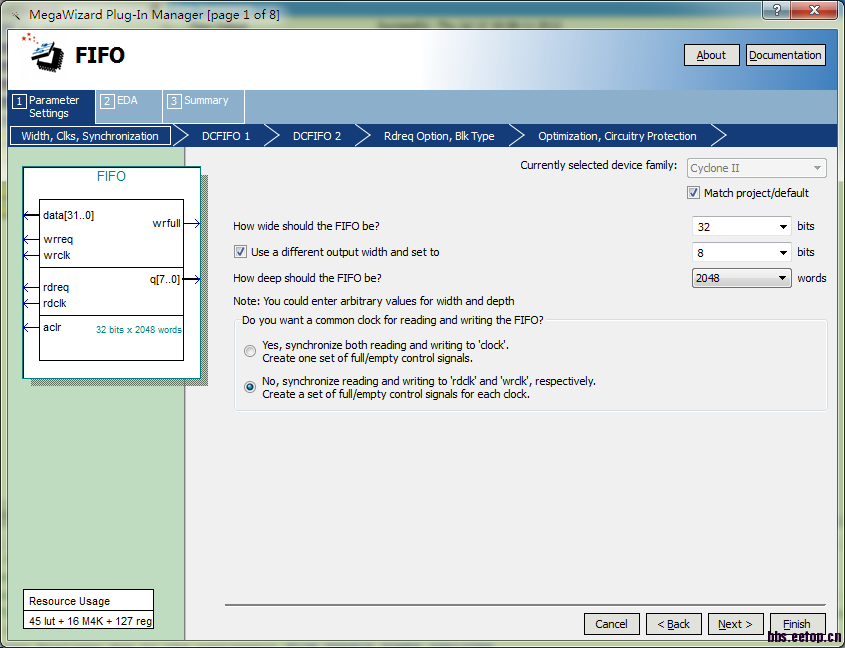

我使用 MegaWizard 添加了 1个FIFO RAM,这个FIFO 我使用了输入32 bits, 输出8 bits,FIFO Deep 设置为 2048 如下图:

设置完成后,并加入VHDL程序,进行编译后,Total memory bits 只显示32768 bits,也就是1024 words,不是设置的2048,

之后我修改 Deep 为512, 编译正常,就算将deep 设置 为更大,编译后仍然是32768 bits (1024 words)。

有哪位能告知其中原因吗?是否有设置参数决定了FIFO 不能超过 1024 x 32bits?

谢谢!

我使用 MegaWizard 添加了 1个FIFO RAM,这个FIFO 我使用了输入32 bits, 输出8 bits,FIFO Deep 设置为 2048 如下图:

设置完成后,并加入VHDL程序,进行编译后,Total memory bits 只显示32768 bits,也就是1024 words,不是设置的2048,

之后我修改 Deep 为512, 编译正常,就算将deep 设置 为更大,编译后仍然是32768 bits (1024 words)。

有哪位能告知其中原因吗?是否有设置参数决定了FIFO 不能超过 1024 x 32bits?

谢谢!

感觉FIFO不是很可靠,不建议使用。我一直都用的是RAM

EP2C5 有多少片上RAM?

计算机中的数据都是以0和1来表示的,其中一个0或者一个1称之为一位,8位称为一个字节(Byte),两个字节称为一个字(Word),4个字节称为双字(Dword)。

我觉得是你设置的时候使用的是M4K来实现FIFO。M4K只有4K=4*1024*8=32768bit,所以高于32768bit的FIFO不能实现了。