MIG 3.9核输出的信号问题

时间:10-02

整理:3721RD

点击:

MIG 3.9 核输出的 app_rdy 信号,拉高时表明 MIG 核准备好接收命令和地址,为低时表明此时输入的命令和地址无效。

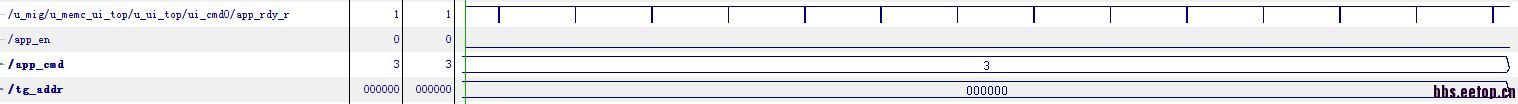

第一副图是我在未输入任何命令和地址的情况下,用 Chipscope 采到的样本,可以发现在未输入任何命令和地址的情况下, app_rdy 信号规律的被拉低(出现逆程)。

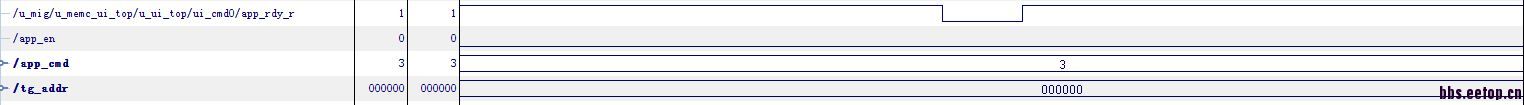

第二副图是 app_rdy 信号逆程的放大。

请问各位大大, app_rdy 信号在不做任何操作的情况下出现逆程的原因?

这些逆程对我输入命令与地址的操作造成了很大的麻烦,因为不知道它什么时候一拉低,命令和地址就无效了,会造成丢数。

请问如何在 app_rdy 信号不规律的情况下,将命令与地址完整的输入 MIG 核?

急求啊!

输入有效命令的时候判断Appready信号有效,只要有效的状态下输入命令,命令就不会丢失。

您好!我明白您的意思,但具体操作的时候由于 app_rdy 信号拉高时间不够长(可能只有一个时钟周期),当我判断其为高时,用非阻塞语句为命令与地址赋值,当下个周期,地址与命令实际输入时, app_rdy 信号已经拉低了,导致地址与命令无效。

总而言之,我用的是 back_to_back 连续读写模式,app_rdy 信号不能在我需要的时间段内一直保持高。

请问有什么办法可以解决么?

你好。具体你的时序我不是很明白,但是你说的当实际命令来时app ready已经无效的情况,可以提前准备好命令挂在MIG的用户接口上,一旦app ready有效,就是命令写入的同时。

谢谢您,您的意思我大概明白,但具体的逻辑我脑子里没有清晰地想法。

能不能麻烦您简单的举个例子?

可以把要发的命令先挂在一个FIFO中,读侧有个选项可以是常态有效。(read through?)

这样你就只要跟FIFO的写侧打交道了。应该明白了吧。还不必担心因过重组合逻辑造成的时序问题。

您好!您说的读侧的常态有效,是指令读使能(rd_en)一直有效么?

不是。fifo有个功能,当你写入有效数据后即使不用read enable也输出第一个有效数据。这个生成fifo的有选项的啊。read enable有效后,read口挂的是下一个被写进的有效数据。我感觉我这样解释好不专业,自己摸索下吧。或者身边有熟悉xilinx FPGA的人应该有知道。

谢谢您了,我自己试试