verilog里面for不能嵌套么?

我搭建testbench的时候用for循环,总跑第二个for第一个不动为什么?

for(i=0;i<=3;i=i+1)

begin

#1 A=A+i;

for(j=0;j<=3;j=j+1)

begin

#1 B=B+j;

end

end

for(j=0;j<=3;j=j+1)

begin

i=i+1;

#1 B=B+j;

end

你在内部的循环里面 i=i+1;

第一次for后 i = 2 了

程序执行是对的

你把第二个循环里的i改为j,这样才符合你的意思。这程序是对的,但不是你的原意。

第二个i = i+1要来做什么,

骚年,C没学过么

那个是多于的我知道,上程序的时候着急没看,我不加还是第一个循环走不了

第一个还是走不动,总在I=0处。

你在第二个循环里面,把每个变量都dispaly出来,看下

还有, i, j 的变量类型貌似也是需要的搞一下的

最好先给A,B 赋初值。

for(int i=0;i<=3;i=i+1)

begin

#1 A=A+i;

for(int j=0;j<=3;j=j+1)

begin

#1 B=B+j;

end

end

i,j是reg verilog里面不知道可以不可以用int?

复过初值了,只是这里没贴出来。

i和j可以使integer吧!

路过,顶一下

你是对的。谢了

module fort (pout,po);output reg[6:0]pout,po;

module fort (pout,po);output reg[6:0]pout,po;

reg [6:0] i,j;

//reg clk;

initial begin

po =0;

pout =0;

end

// initial clk =0;

// always #5 clk = !clk;

always begin

for (i = 0;i < 6'b1000_00; i = i + 1)

begin

#1 po = po+i;

for (j=0;j<6'b0000_11;j = j+1)

#1 pout = pout + j;

end

end

endmodule

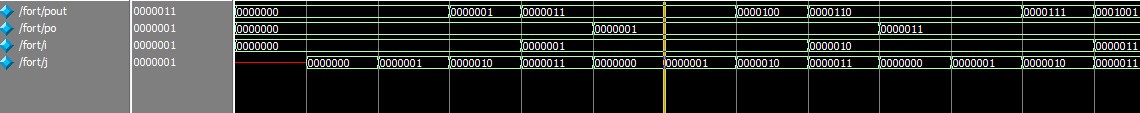

小编我这样写的代码是没有问题的,不知道你用什么仿真的,我用的是modelsim 6.5,程序中使用initial同样可以,我的波形如图:

学习,学习,再学习!

我用reg定义i不行啊。只能用integer。我的是modelsim6.5e

貌似这个写法,综合会有些问题吧。

是测试的时候用的。

你再试试吧,我也是用的6.5e但是我仿出结果了啊!

楼上几位正解