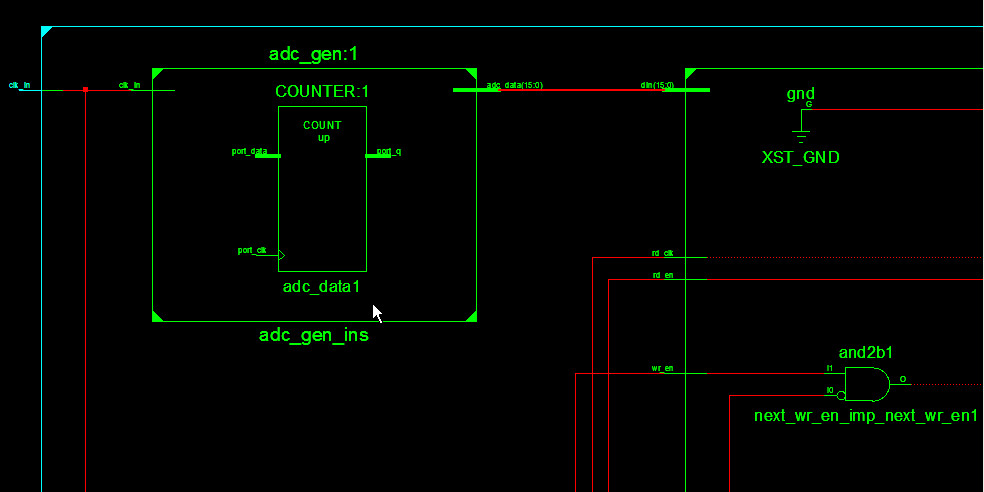

ISE综合后RTL图错误

图中clk_in进入adc_gen模块后没有接任何连线,adc_gen模块的输出到后一模块中也没有接任何连线。

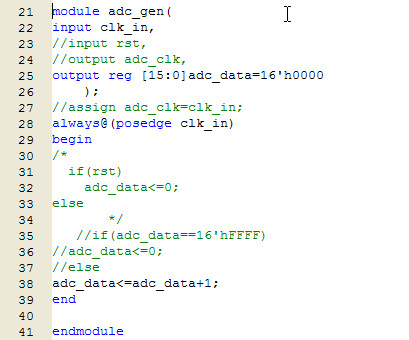

这是adc_gen模块的代码,在ISE10.1中综合完全正常,在13.1中综合不正常。

求教各位高手有没有遇到过这种情况?

顶一个 。

一定不能用复位信号?还是推荐用规范代码,而不是放在看综合器如何使用上的。对XILINX器件FAE推荐同步复位,同步解复位,与ALTERA的不太一样。

跟复位没关系,加了复位信号还是一样

这里显示的应该是一整个模块,详细电路应该是双击adc_gen_ins进去看

我也出现这种状况,时序仿真是正确的,但rtl视图上有些引脚就是没连上,我编了一个小程序试了试,输入为16位,当输出为16位时,rtl输入引脚连接上了,但为虚线,当输出为32位时,输入引脚就没连接上,很奇怪啊,ise 为13.1

求解答

因为代码在单位的电脑上,无法黏贴,因此写个简单的程序,表达下我想表达的东西

程序中req1,req2没有进行同步处理,我原程序对他们采用脉冲边缘检测法进行过检测

model tx(

input clk,

input rst_n,

input req1,

input req2,

input [15:0] datain,

output [31:0] dataout

);

always@(posedge clk or negedge rst_n)

begin

if(!rst_n) word32<=0;

else

begin

if(req1==1) word32[15:0]<=datain;

if(req2==1) word32[31:0]<=datain;

end

end

assign dataout=word32;

endmodel

rtl中datain没有和任何管脚连接,若将dataout改为[15:0],datain就和寄存器连接上了,但为虚线

已解决,见http://forums.xilinx.com/xlnx/board/crawl_message?board.id=Spartan&message.id=14064