modelsim仿真时module不在test下面,如何解决?

时间:10-02

整理:3721RD

点击:

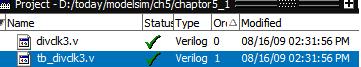

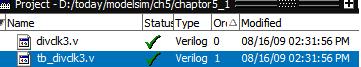

各位达人,我用modelsim仿真时,module文件为divclk3.v,测试文件为tb_divclk3.v。

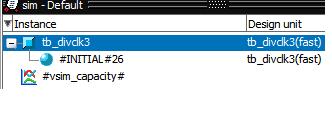

在project里面,正常显示如下图:

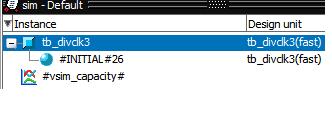

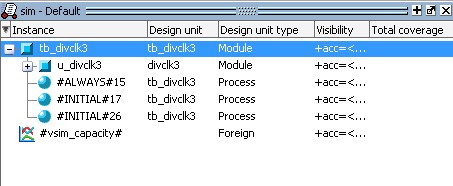

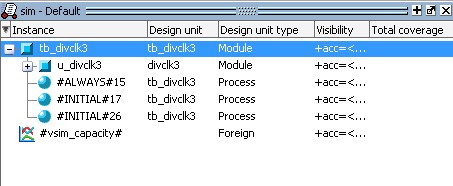

当我仿真的时候,却出现奇怪的事情,那就是tb_divclk3并不包含divclk模块,真是郁闷啊。如下图所示。

有人知道怎么解决这个问题么,若知道就高速我,让我好好努力学习啊。真是谢谢。

后面附上这两个文件的源程序。

divclk3.v文件如下:

tb_divclk3.v文件如下:

在project里面,正常显示如下图:

当我仿真的时候,却出现奇怪的事情,那就是tb_divclk3并不包含divclk模块,真是郁闷啊。如下图所示。

有人知道怎么解决这个问题么,若知道就高速我,让我好好努力学习啊。真是谢谢。

后面附上这两个文件的源程序。

divclk3.v文件如下:

- `timescale 1ns/1ns

- `define DLY 0

- `define DLY1 0

- `define DLY2 0

- module divclk3(

- clk_in,

- rst_in,

- clk_out

- );

- input clk_in;

- input rst_in;

- output clk_out;

- reg clk_out;

- reg clk_n;

- reg clk_not;

- reg d1;

- reg d2;

- reg clk_s;

- always @(posedge clk_in or negedge rst_in)begin

- if(~rst_in)

- d1 <= #`DLY 1'b0;

- else

- d1 <= #`DLY clk_not;

- end

- always @(posedge clk_n or negedge rst_in)begin

- if(~rst_in)

- d2 <= #`DLY 1'b0;

- else

- d2 <= #`DLY d1;

- end

- always @(posedge clk_s or negedge rst_in)begin

- if(~rst_in)

- clk_out <= #`DLY 1'b0;

- else

- clk_out <= #`DLY d2;

- end

- always @(clk_out)

- clk_not <= #`DLY1 ~clk_out;

- always @(clk_in)

- clk_n <= #`DLY1 ~clk_in;

- always @(clk_out or clk_in or clk_n)begin

- if(clk_out)

- clk_s <= #`DLY2 clk_in;

- else

- clk_s <= #`DLY2 clk_n;

- end

- endmodule

tb_divclk3.v文件如下:

- `timescale 1ns/1ns

- `define DLY 0

- module tb_divclk3;

- reg clk_in;

- reg rst_in;

- wire clk_out;

- divclk3 u_divclk3(

- .clk_in(clk_in),

- .rst_in(rst_in),

- .clk_out(clk_out)

- );

- always #100 clk_in <= ~clk_in;

- initial begin

- rst_in=1;

- clk_in=1;

- #200;

- rst_in=0;

- #200;

- rst_in=1;

- end

- initial begin

- $dumpfile("wave.dump");

- $dumpvars(0,tb_divclk3);

- #100000;

- $stop;

- end

- endmodule

你实现的是三分频吧,三分频没有这么实现的啊。你可以看看这篇文章http://blog.sina.com.cn/s/blog_6f3d37ff0100umaf.html

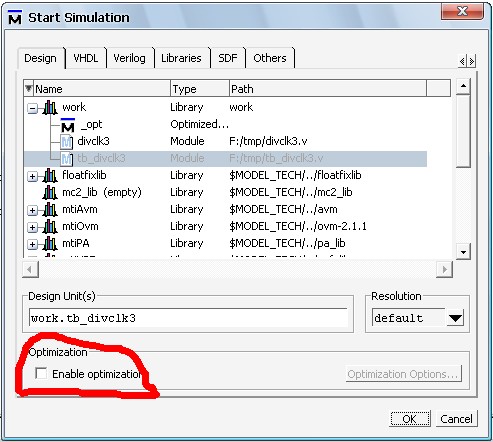

如果非要解决你modelsim没有模块的问题,可以在进行simulate的时候,去掉优化,就可以了。

非常感谢你,你解决了困扰我多天的问题,让我学习再上台阶。

你是资深的电子专家,我要好好向你学习。

嗯,原来去掉优化这么有用!以前只是知道一定要去掉,还不清楚为什么。